#### 工學碩士 學位論文

# 다중 포트 증폭기의 진폭 및 위상 제어에 관한 연구

A study on the control of amplitude and phase of multiport amplifier

2012년 8월

村舎市立大學校 大學院 電子電氣컴퓨터 工學科 林 銀 天

### 다중 포트 증폭기의 진폭 및 위상 제어에 관한 연구

A study on the control of amplitude and phase of multiport amplifier

指導教授 李 文 揆

이 論文을 工學碩士學位 論文으로 提出함

2012년 6월

서울市立大學校 大學院

電子電氣컴퓨터 工學科

林 銀 天

林 銀 天 의 工學碩士學位 논문을 인준함.

# 심사 위원장인심 사 위 원인

인

2012년 6월

심사위원

서울市立大學校 大學院

#### 국 문 초 록

최근 위성 복합탑재체 설계에서 다중 포트 전력 증폭기가 이용된다. 다중 포트 증폭기는 송출 전력을 가변할 수 있고, 고장에 대해 둔감하다. 특별히, K-대역과 같은 고주파에서 이용되는 MPA의 PA들은 개별적인 특성이 다르고, RF 회로로이를 제어하기에는 구현이 복잡하고 이상적인 특성을 얻기 어렵다.

이 연구에서 제안하는 I-Q 보정 알고리즘은 RF 신호 경로에 적용된 가변 위상 천이기와 감쇄기의 전압을 제어함으로써 MPA 출력 포트 간의 높은 격리도를 가능하게 한다. 알고리즘은 위상 및 진폭 부정합을 찾기 위해 개발되었고, Altera社 의 EP3C25Q240C8N Cyclone III FPGA 칩에 프로그래밍 되었다. 제안한 알고리즘의 시연을 위한 프로토타입 모듈로 UHF-대역 MPA 블록과 7-포트 복조기를 이용한 보정 블록을 설계했다. 7-포트 복조기 구조는 고주파 신호를 기저대역 신호를 중간 주파수 없이 변경한다.

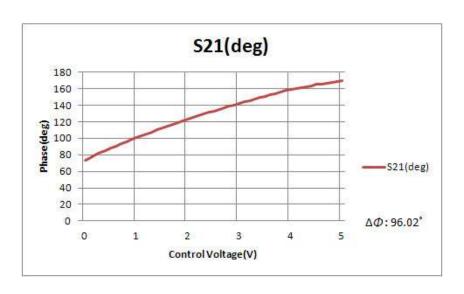

전압 제어 위상 천이기는 1.04dB의 삽입 손실을 가지고 96.02도 범위에서 위상을 변경한다. 전압 제어 감쇄기는 0.6도의 위상 천이를 가지며 1.17dB에서 3.1dB의 삽입 손실 값을 가변한다. 위상 천이기와 감쇄기를 제어하는 두 DAC 전압은 FPGA에서 생성된다. DAC 출력 버퍼에서 나오는 위상 천이기와 감쇄기의 전압은 그 가변에 따라 RF 신호 경로 상의 감쇄와 위상 오차 값을 결정한다.

첫째 알고리즘은 전체 계산 중에 높은 정밀도를 유지하기 위해 부동 소수점형 숫자들을 이용한다. 부동 소수점형 숫자를 이용한 직접적인 atan과 제곱근 함수 구현은 단순하고 직관적이다. 하지만, 효율과 자원 소모는 FPGA 장치에 적합화(fitting) 하기엔 너무 크다. 적절한 자원 사용을 위해 부동 소수점형 숫자를 이용하는 대신 고정 소수점형 숫자들을 이용한다. 이에 더해, 더 높은 효율성을 위해서, atan과 제곱근 함수를 직접 구현하는 대신 근사화된 방법을 성공적으로

적용했다.

최종 전체 경로 테스트는 알고리즘의 성능과 가능성을 보인다. 총 두 번의 전체경로 테스트를 수행했으며 다른 입력 전력 값과 다른 종류의 복조기로 테스트했다. 가변 타입 복조기를 위한 첫째 테스트 설정은 다음의 파라미터를 가진다: 916MHz의 4.48dBm 입력 RF 전력, 917MHz의 8.53dBm 입력 LO 전력, 2.38V의 위상천이 전압, 그리고 0.523V의 감쇄기 전압. 제안하는 알고리즘을 사용하여, 우리는최대 47.74dB, 일반적으로 20dB 이상의 포트 간 격리도를 얻었다. 고정 타입복조기를 위한 테스트 설정은 다음의 파라미터를 가진다: 916MHz의 -12.44dBm 입력 RF 전력, -82.5도의 복조기 위상 천이 오프셋. 그리고 나머지는 가변 타입복조기와 동일한 설정이다. 실험 결과는 최대 40.0dB, 일반적으로 18.0dB의격리도를 보인다.

결론적으로, 알고리즘은 UHF 대역의 7-포트 복조기와 MPA 프로토타입 모듈로부터 RF 동위상, 90도 위상의 신호의 이상적인 위상과 진폭을 찾을 수 있음을 보인다.

주요어(Keywords): 다중포트증폭기(MPA), 격리도, 위성 발사체, 버틀러 행렬, IQ 보정 알고리즘, 변복조기 회로, FPGA, VHDL

#### 工學碩士 學位論文

# 다중 포트 증폭기의 진폭 및 위상 제어에 관한 연구

A study on the control of amplitude and phase of multiport amplifier

2012년 8월

村舎市立大學校 大學院 電子電氣컴퓨터 工學科 林 銀 天

#### 목 차

| 목 ᅔ            | ት     |                                | i |

|----------------|-------|--------------------------------|---|

| 그림             | 목차    | j                              | V |

| 亚 <sub>巨</sub> | 락차    | i                              | X |

| 용어             | 및 약여  | 어 설명                           | X |

| 제 1            | 장     | 서론                             | 1 |

|                | 제 1 절 | 다중 증폭기 개요                      | 1 |

|                | 제 2 절 | 연구의 필요성                        | 5 |

|                | 제 3 절 | 다중 포트 증폭기 동작 원리                | 7 |

|                | 제 4 절 | 기존 보정 방식의 예1                   | 3 |

|                |       | 다중 포트 증폭기 출력 포트간 격리 향상을 위한 제인1 |   |

|                | 제 1 절 | 제안하는 구조1:                      | 5 |

|                | 제 2 절 | 검증용 UHF 대역 다중 포트 증폭기 블록1       | 7 |

|                | 제 3 절 | 검증용 UHF 대역 7-포트 복조기 블록19       | 9 |

|                | 제 4 절 | 3-dB 커플러                       | 2 |

|                | 제 5 절 | 위상 천이기24                       | 4 |

|                | 제 6 절 | 감쇄기29                          | 9 |

|                | 제 7 절 | 전력 증폭기                         | 3 |

|                | 제 8 절 | 출력 결합을 위한 10-dB 커플러34          | 4 |

| 제 9 절 7-포트 상관기3                                    |

|----------------------------------------------------|

| 제 10 절 정밀 I-Q 전력 분배기3                              |

| 제 11 절 전력 검출기4                                     |

| 제 12 절 수동 보정 측정 결과4                                |

| 제 3 장 격리도 향상 보정 알고리즘 FPGA 회로5                      |

| 제 1 절 FPGA 보드5                                     |

| 제 2 절 활성 직렬 프로그래밍 방식5                              |

| 제 3 절 JTAG 프로그래밍 방식 설명5                            |

| 제 4 절 ADC 입력 드라이버6                                 |

| 제 5 절 DAC 출력 버퍼6                                   |

| 제 4 장 다중 포트 증폭기의 포트 간 격리 향상을 위한 보정 약<br>고리즘6       |

| 제 1 절 보정 알고리즘 개요6                                  |

| 제 2 절 ADC 데이터의 부동 소수점 숫자 변환7                       |

| 제 3 절 진폭 계산의 부동 소수점 숫자 방식 구현7                      |

| 제 4 절 ATAN2의 부동 소수점 숫자 방식 구현7                      |

| 제 5 절 위상 계산의 부동 소수점 숫자 방식 구현8                      |

| 제 6 절 ADC 데이터의 고정 소수점 숫자 변환8                       |

| 제 7 절 진폭 계산의 고정 소수점 숫자 방식의 구현8                     |

| 제 8 절 Alpha Max Beta Min 크기 예상 고정 소수점 숫자 방수구현[21]8 |

| 제 9 절 자가 정규화 ATAN2 고정 소수점 숫자 방식 구현[22]9            |

| 제 10 절 전체 IQ 보정 알고리즘의 고정 소수점 숫자 |     |

|---------------------------------|-----|

| 현                               | 93  |

| 제 11 절 NCO의 구현                  | 95  |

| 제 12 절 입력되는 I와 Q 채널 신호의 확인      | 98  |

| 제 5 장 MPA 검증 모듈의 측정             | 101 |

| 제 1 절 전체 구성                     | 101 |

| 제 2 절 측정 결과                     | 103 |

| 제 6 장 결론                        | 108 |

| 참 고 문 헌                         | 110 |

| Abstract                        | 112 |

#### 그림 목차

| 그림 1-1 위성 발사체 출력 부분1                                  |

|-------------------------------------------------------|

| 그림 1-2(a) ETS-6 위성 (b) ETS-6 위성 탑재 장비 블록도[11]2        |

| 그림 1-3(a) 키주나(WINDS) 위성 (b) Ka-대역 MPA[11]3            |

| 그림 1-4 (a) 전통적인 빔포밍 안테나 (b) MPA를 적용한 빔포밍 안테<br>나[11]5 |

| 그림 1-5 4x4 다중포트 증폭기의 동작 원리[12, 14]7                   |

| 그림 1-6 다중포트 증폭기의 단일 경로 동작7                            |

| 그림 1-7 위상 오프셋과 격리도 관계10                               |

| 그림 1-8 진폭 비율과 격리도 관계11                                |

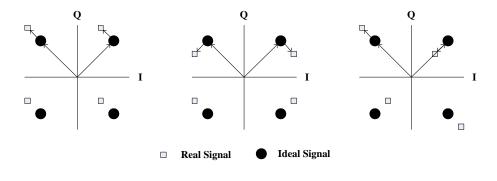

| 그림 1-9 IQ 오류의 예[15]11                                 |

| 그림 1-10 기존 보정 방식의 예[16]13                             |

| 그림 2-1 제안하는 다중 포트 증폭기 출력 포트 간 격리 향상을 위<br>한 구조의 블록도15 |

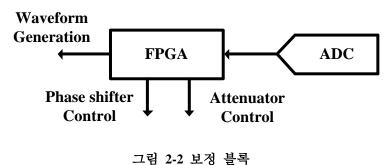

| 그림 2-2 보정 블록16                                        |

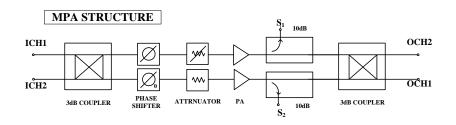

| 그림 2-3 검증을 위한 MPA 구조 블록도17                            |

| 그림 2-4 검증용 UHF 대역 MPA 블록17                            |

| 그림 2-5 검증용 UHF 대역 7-포트 복조기 블록도19                      |

| 그림 2-6 조정된 복조기의 성상도20                                 |

| 그림 2-7 제작한 검증용 UHF 대역 7-포트 복조기21                      |

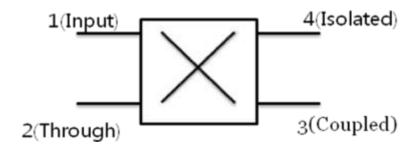

| 그림 | 2-8 3-dB 커플러의 포트 기능                                      | 22 |

|----|----------------------------------------------------------|----|

| 그림 | 2-9 RCP890Q03 커플러                                        | 22 |

|    | 2-10 3-dB 커플러의 S-파라미터 (b) 3-dB 커플러의 위상 (c)<br>-류 (d) 지향도 |    |

| 그림 | 2-11 전압 가변형 위상 천이기 블록도                                   | 24 |

| 그림 | 2-12 전압 가변형 위상 천이기 회로도                                   | 25 |

| 그림 | 2-13 전압 가변형 위상 천이기 위상 계산을 위한 블록도[17]                     | 25 |

| 그림 | 2-14 전압 변화에 따른 위상 천이(deg)                                | 27 |

| 그림 | 2-15 고정형 위상 천이기                                          | 27 |

| 그림 | 2-16 제작한 가변형 및 고정형 위상 천이기                                | 28 |

| 그림 | 2-17 가변형 감쇄기                                             | 29 |

| 그림 | 2-18 전압 가변형 감쇄기 회로도                                      | 30 |

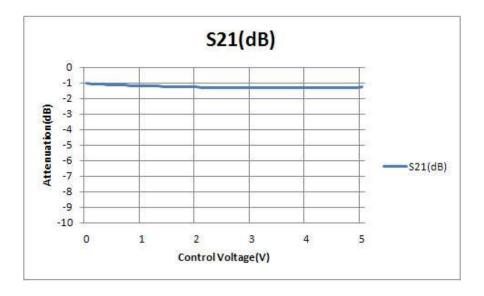

| 그림 | 2-19 전압 변화에 따른 감쇄(dB)                                    | 31 |

| 그림 | 2-20 고정형 감쇄기 블록도                                         | 32 |

| 그림 | 2-21 제작한 가변형 및 고정형 위상 천이기                                | 32 |

| 그림 | 2-22 전력 증폭기 회로도                                          | 33 |

| 그림 | 2-23 제작한 전력 증폭기                                          | 33 |

| 그림 | 2-24 10-dB 커플러                                           | 34 |

| 그림 | 2-25 제작한 10-dB 커플러                                       | 34 |

| 그림 | 2-26 (a) 10-dB 커플러의 S-파라미터 (b) 10-dB 커플러의 위상.            | 35 |

| 그림 | 2-27 복조를 위한 7-포트 상관기 구조                                  | 36 |

|    | 2-28 (a) 7-포트 상관기 위상 측정 (b) 7-포트 상관기 크기 측   |    |

|----|---------------------------------------------|----|

|    | 2-29 정밀한 I-Q 신호 분배기                         |    |

| 그림 | 2-30 (a) 보상하기 전의 위상 차이 (b) 보상 후의 위상 차이      | 38 |

| 그림 | 2-31 제작한 정밀 전력 분배기                          | 39 |

|    | 2-32 전력 분배기의 반사 손실과 격리도 (b) 위상과 크기 차        |    |

| 그림 | 2-33 전력 검출기 회로도                             | 41 |

| 그림 | 2-34 RF 입력 전압 비 출력 전압                       | 41 |

| 그림 | 2-35 제작한 전력 검출기                             | 42 |

| 그림 | 2-36 하모닉 성분의 발생                             | 44 |

| 그림 | 2-37 최종 전력 검출기 회로도                          | 44 |

| 그림 | 2-38 하모닉이 제거된 신호                            | 45 |

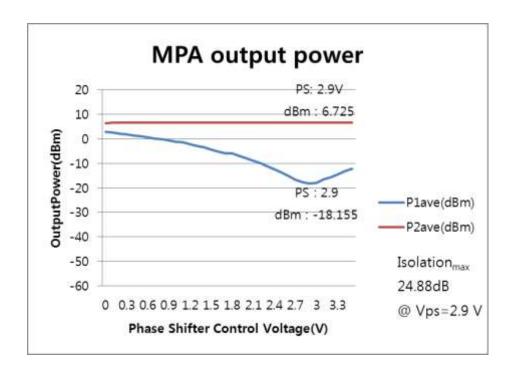

| 그림 | 2-39 위상 천이기 전압 가변시 MPA 출력 전력                | 46 |

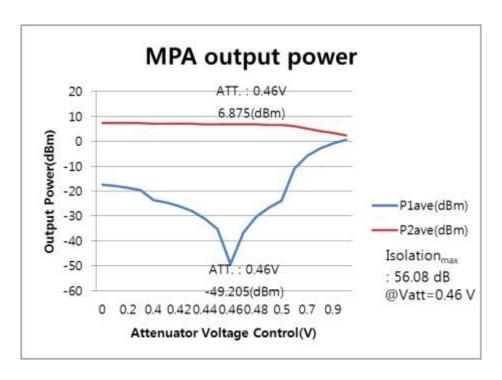

| 그림 | 2-40 감쇄기 전압 가변시 MPA 출력 전력                   | 47 |

| 그림 | 2-41 수동 보정 전 MPA 출력 파형                      | 48 |

| 그림 | 2-42 수동 보정 후 MPA 출력 파형                      | 49 |

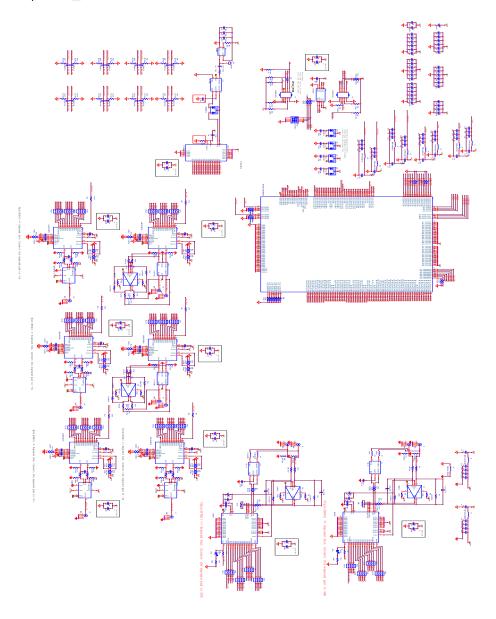

| 그림 | 3-1 IQ 보정 FPGA 보드 회로도                       | 50 |

| 그림 | 3-2 제작한 IQ 보정을 위한 FPGA 보드                   | 51 |

| 그림 | 3-3 Altera社의 EP3C25Q240C8N FPGA 칩의 핀 연결 회로도 | 52 |

| 그림 | 3-4 MSEL의 선택을 통한 프로그래밍 모드 선택                | 53 |

| 그림 | 3-5 단일 장치 활성 시리얼 설정 방식의 블록도                 | 55 |

| 그림 | 3-6 단일 장치 활성 직렬 설정 방식 회로도             | 56 |

|----|---------------------------------------|----|

| 그림 | 3-7 코드를 저장하기 위한 PROM                  | 56 |

| 그림 | 3-8 JTAG 설정 방식의 블록도                   | 57 |

| 그림 | 3-9 IEEE 1149.1 BST 회로(EPC16)[18]     | 58 |

| 그림 | 3-10 IEEE 1149.1 BST 회로의 상태 머신도[18]   | 59 |

| 그림 | 3-11 JTAG 설정 방식의 회로도                  | 60 |

| 그림 | 3-12 ADC 입력 드라이버                      | 61 |

| 그림 | 3-13 ADC 입력 드라이버 블록도                  | 64 |

| 그림 | 3-14 사인 코사인 생성을 위한 차동 DAC 출력 버퍼       | 66 |

| 그림 | 3-15 차동 DAC 출력 버퍼 블록도                 | 66 |

| 그림 | 3-16 제어 신호 생성을 위한 싱글 엔드 DAC 출력 버퍼     | 67 |

| 그림 | 4-1 이상적인 경우의 샘플링 데이터 시뮬레이션            | 68 |

| 그림 | 4-2 한 라운드의 알고리즘                       | 69 |

| 그림 | 4-3 32비트 정수의 binary32 형태 변환 회로 블록도    | 71 |

| 그림 | 4-4 32비트 정수의 binary32 형태 변환 시뮬레이션     | 74 |

| 그림 | 4-5 32비트 정수 최대값의 binary32 형태 변환 시뮬레이션 | 74 |

| 그림 | 4-6 32비트 정수 최소값의 binary32 형태 변환 시뮬레이션 | 75 |

| 그림 | 4-7 진폭 계산의 부동 소수점 숫자 방식 구현 블록도        | 76 |

| 그림 | 4-8 ATAN2의 부동 소수점 숫자 방식 구현의 블록도       | 78 |

| 그림 | 4-9 위상 계산의 부동 소수점 숫자 방식 구현 블록도        | 80 |

| 그림 | 4-10 진폭 오차 시뮬레이션                      | 88 |

| 그림 4-11 시뮬레이션 데이터 생성을 위한 Texas Instrument社의 평가<br>보드       |

|------------------------------------------------------------|

| 그림 4-12 평가 보드에서 샘플링한 데이터89                                 |

| 그림 4-13 위상 오차 시뮬레이션92                                      |

| 그림 4-14 전체 IQ 보정 알고리즘 구현93                                 |

| 그림 4-15 NCO 블록도95                                          |

| 그림 4-16 NCO의 동작 방식95                                       |

| 그림 4-17 NCO 1MHz 사인 코사인 생성 시뮬레이션97                         |

| 그림 4-18 ADC-DAC 직접 연결 블록도98                                |

| 그림 4-19 ADC에 입력된 1MHz 복조된 사인 코사인 파형99                      |

| 그림 4-20 평균을 취해 임펄스 신호를 줄인 복조 신호의 성상도. 100                  |

| 그림 5-1 IQ 보정 알고리즘 검증을 위한 실험 구성(가변형 복조기)                    |

| 그림 5-2 IQ 보정 알고리즘 검증을 위한 실험 구성(고정형 복조기 +<br>디지털 위상 오프셋)102 |

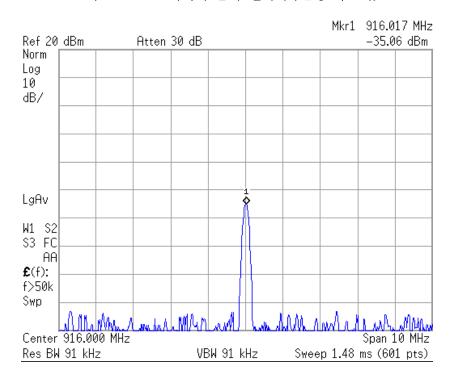

| 그림 5-3 OCH1에서의 출력 전력 (가변형 복조기)104                          |

| 그림 5-4 OCH2에서의 출력 전력 (가변형 복조기)104                          |

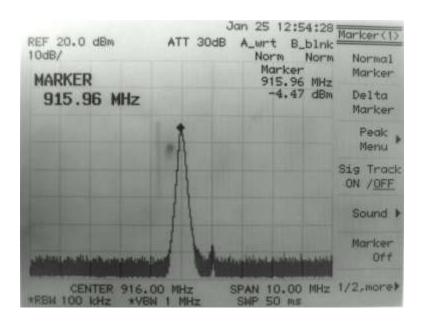

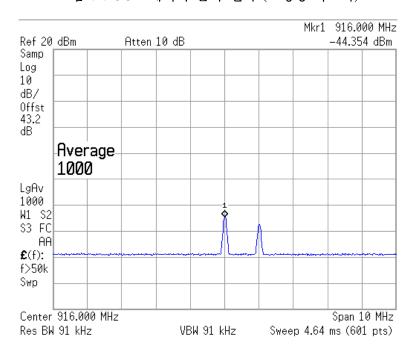

| 그림 5-5 OCH1에서의 출력 전력 (고정형 복조기)105                          |

| 그림 5-6 OCH2에서의 출력 전력 (고정형 복조기)105                          |

| 그림 5-7 알고리즘 적용 전의 MPA 출력 신호106                             |

| 그림 5-8 알고리즘 적용 후의 MPA 출력 신호107                             |

#### 표 목차

| 丑 | 3-1 프로그래밍 설정 방식                        | 53             |

|---|----------------------------------------|----------------|

| 丑 | 3-2 주요 설정 핀 설명                         | 54             |

| 丑 | 4-1 AD6646의 입력 범위                      | 71             |

| 丑 | 4-2 메가 함수 구현시 에상되는 자원 사용량              | 75             |

| 丑 | 4-3 진폭 계산의 부동 소수점 숫자 방식 구현 자원 소모       | 76             |

| 丑 | 4-4 ATAN2의 부동 소수점 숫자 방식 자원 소모          | 79             |

| 丑 | 4-5 위상 계산의 부동 소수점 숫자 방식 구현의 자원 소모 8    | 30             |

| 丑 | 4-6 고정 소수점 연산 후 변화된 벡터 크기              | 32             |

| 丑 | 4-7 진폭 계산의 사용 자원(3.28 비트 고정형 숫자인 경우) 8 | 33             |

| 丑 | 4-8 진폭 계산의 사용 자원(3.14 비트 고정형 숫자인 경우) 8 | 33             |

| 丑 | 4-9 Alpha Beta 파라미터 별 오차 범위 테스트 결과     | 36             |

| 丑 | 4-10 Alpha Max Beta Min 알고리즘 구현의 자원 사용 | 37             |

| 丑 | 4-11 자가 정규화 ATAN2 알고리즘 자원 사용9          | €2             |

| 丑 | 4-12 전체 알고리즘에서 사용한 자원                  | <del>)</del> 4 |

| 丑 | 4-13 NCO 구현의 소모 자원9                    | €7             |

| 丑 | 5-1 가변형 복조기를 이용한 측정 결과10               | )3             |

| 丑 | 5-2 고정형 복조기를 이용한 측정 결과10               | )3             |

#### 용어 및 약어 설명

- 유효등방성 복사전력(Equivalent/Effective Isotropically Radiated Power, EIRP): 최대 안테나 이득 방향으로 관찰되는 최대 전력 밀도를 생성하기 위해 송출되는 이론적인 등방성 안테나의 전력 양이다. 즉, 최대 전력 에너지를 동등하게 분산시켜 환산한 출력 전력을 나타낸다. Pt(송신안테나의 입력전력) \* G(안테나 최대 이득)로 표현된다. 안테나의 종류, 크기, 형태와 상관없이 성능 평가 척도로 이용된다.

- 등방성 안테나(Isotropic Antenna): 모든 방향으로 동일한 양으로 분산된 파워를 송출하는 이론적인 안테나이다.

- 버틀러 행렬(Butler matrix): 빔형성 네트워크의 종류 중 하나이다. 어떠한 입력 포트에 신호가 인가 되느냐에 따라서, 안테나의 빔 방향이 한 평면 상에서 특정 방향으로 지향되게 된다. 버틀러 행렬이 두 층으로 합쳐진다 면 3차원 스캐닝이 가능해진다. 이는 위상 배열 안테나와 동일한 역할을 수행하게 된다.

- 스퀘어 법칙(Square-law) 영역: 특정 전력 레벨에 대해서, 검출기의 출력 전압은 그것의 와트 단위의 측정된 전력에 비례한다. 선형 동작에서, 옴 의 법칙에 따라 전압이 전력의 제곱근(square root)여야 한다. 그러므로, 선 형 동작 영역인 이 영역에서는 전력이 전압의 제곱이다.

- 지향도(Directivity): 커플러는 방향성 결합기로 격리도의 높은 정도를 나타내는 성능 평가 척도이다. 격리도에서 커플링이나 삽입 손실 값을 빼서계산할 수 있다.

- 오버슈트(overshoot): 펄스 파형을 나타낼 때 사용하는 말로, 어느 회로의 입력으로서 구형파를 가한 경우에 과도 특성에 의해서 출력 파형의 상승 부에 생기는 리플을 말한다.

- 유한상태기계(Finite State Machine): 직접적인 의미는 유한 개수 상태를 가진 기계이다. 특징은 다음과 같다. 유한 수의 상태를 가진다. 자신의 상태를 시험할 수 있다. 외부로부터 입력을 받을 수 있다. 이산된 시간의 단계에 따라 자기 자신의 상태가 변화한다. 현재 상태와 외부 입력을 조합하여 규칙에 따라 상태가 변화한다.

#### 제1장 서론

#### 제 1 절 다중 증폭기 개요

최근 위성 통신 탑재체의 설계는 유연성에 많은 노력을 기울이고 있다. 복합탑재체의 출력부 구현을 위해 필요한 기술은 최적화된 안테나, 빔 포밍의 유연성을 위한 디지털 프로세서, 최적의 효율을 가진 반도체 전력 증폭기들(Solid State Power Amplifier, SSPA)이다.

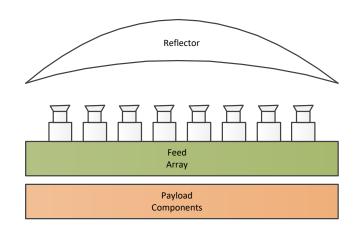

먼저, 최적화된 안테나를 구현하기 위해서 안테나 피드 어레이와 반사기(reflector)는 전파 반경(coverage)에 대해서 사용자 링크의 집중 빔(spot beam)을 연속적으로 생성할 수 있어야 한다.

그림 1-1 위성 발사체 출력 부분

디지털 프로세서는 여러 배열의 빔들을 생성하고 각 빔에 요구되는 대역폭을 지정한다. 또한, 이는 반도체 전력증폭기들을 각 빔들에 대한 최대한의 유효등방성 복사전력 (EIRP)가 할당 되도록 조정한다. 디지털 빔 포머는 디지털 로직만을 변경함으로써 다른 전파 반경을 생성할 수 있는 장점이 있다[01].

마찬가지로, 유연성을 높이기 위한 이러한 작업의 일환으로 다중 포트 전력 증폭기(Multiport Power Amplifier, MPA)에 대한 관심이 고조되고 있다. MPA는 개별 증폭기를 버틀러 행렬(Butler Matrix)로 결합하여 사용하는 방법으로 재구성(reconfigurable)이 가능하고 위성에서 중요한 신뢰성이 높은 특징을 가지고 있다. MPA의 역사는 1960년대로 거슬러 올라가지만, 위성 중계기에 버틀러 행렬[02]을 적용하는 연구는 1974년 Comsat 연구소에서 처음 시도되었다[03].

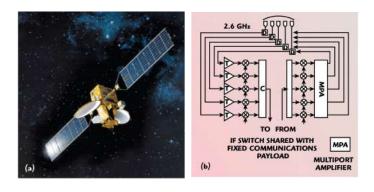

그림 1-2(a) ETS-6 위성 (b) ETS-6 위성 탑재 장비 블록도[11]

최초의 MPA의 적용 사례는 MSAT-2로 불리는 AMSC-1 위성과 MSAT-1로 Hughes 사에 의해서 개발되어 각각 1995년과 1996년에 발사되었으며, 여기에 L-대역하이브리드 매트릭스 증폭기가 이동통신 중계기의 트래픽 경로 재구성을 제공하기위해 적용되었다[04].

그 이후 2003년에 정지궤도 진입에 성공한 ESA(European Space Agency)의 Artemis에는 L-대역 육상 이동(L-band Land Mobile, LLM) 탑재 장비가 포함되었으며 이는 하나의 MPA 기반 송신 회로로 집적하여 유럽 지역을 위한 스팟빔과 세 개의

다른 스팟 빔 사이에서 전환을 지원했다[05-07].

2005년에 European Aeronautic Defense and Space Company (EADS)의 산하 Astrium 은 Inmarsat IV를 개발 및 제작하였으며, 여기에는 9미터까지 펼칠 수 있는 반사기와 광대역 광역 네트윅(Broadband Global Area Network, BGAN) 서비스를 지원하기 위한 복잡한 디지털 신호 처리기가 포함되었으며, 150개의 SSPA가 안테나 송신부로써 동작하며, 15개의 8X8 다중 포트 전력 증폭기로 묶여져 있다[01].

Ka-대역에서 동작하는 위성 통신 시스템의 가장 큰 제한 요소는 강우 감쇄다. 이 문제를 해결하기 위해서 다중빔 적응 안테나(Multi-beam Adaptive Antenna, MAA) 구성에 MPA를 적용하는 연구가 1989년에 제안되었다[08-09].

일본 키주나 위성(Wideband Inter-Networking engineering test and Demonstration Satellite, WIND)가 Ka 대역의 MPA 구성을 구현한 첫 위성이다. 여기에는 효율적인 TWTA에 기반한 고전력 MPA가 이용되어 비가 오는 지역에서도 더 많은 전력을 할당할 수 있게 설계 되었다[10].

그림 1-3(a) 키주나(WINDS) 위성 (b) Ka-대역 MPA[11]

K 대역과 같이 높은 주파수에서 각 개별 증폭기는 증폭기 간 특성이 다르고, 이를 제어하는 RF 회로 구현의 복잡성으로 이상적인 특성을 얻기가 어렵다. 이러한 문제를 해결하기 위해서 본 연구에서는 구현이 단순한 직접변환 방식의하나인 6-포트 변복조 구조를 7-포트로 변환하여 K-대역의 MPA 격리도 개선을위한 보정 회로로 적용하여 문제를 해결한다.

본 논문의 구성은 다음과 같다. 1장에서 MPA의 동작 원리와 포트 간 격리도 향상을 위한 기존 보정방식을 설명한다. 2장은 다중 포트 증폭기 포트 간 격리 향상을 위해 제안하는 구조를 설명한다. 다음 3장에서 제안하는 구조의 격리도 향상을 위한 보정 알고리즘 구현을 위한 FPGA 보드를 설명하고 4장에서 제안하는 구조의 격리도 향상을 위한 보정 알고리즘을 설명하고 5장에서 UHF 대역의 MPA 검증 모듈의 측정을 통해 해당 알고리즘의 이용 가능성을 확인하고 마지막으로 6장에서 결론으로 마무리 한다.

#### 제 2 절 연구의 필요성

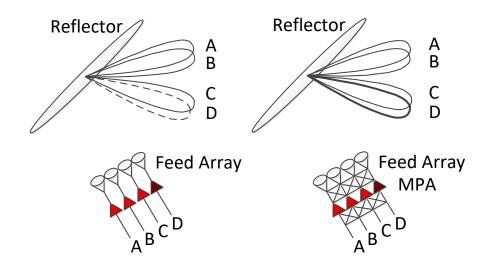

그림 1-4(a) 전통적인 빔포밍 안테나 (b) MPA를 적용한 빔포밍 안테나[11]

최근 위성에서 효율적으로 안테나의 빔 커버리지를 바꾸기 위해 빔형성(beamforming) 안테나를 이용하고 있다. 전통적인 빔형성 안테나는 그림 1-4 (a)와 같이 각 안테나에서 전력증폭기가 직접 연결되는 구조이다. 이 구조의 단점은 A, B, C, D 중 하나의 고 전력 증폭기(High Power Amplifier, HPA)가 동작하지 않으면 해당 빔은 존재하지 않게 된다. 개별 빔 별로 제어될 수 있는 전체 트래픽 내에서 가용부분의 공유 능력은 같은 빔에 할당된 HPA의 크기에 의해 제약을 받는다.

이에 반해, 본 연구에서 다루려는 MPA를 적용한 안테나는 한 범에 할당된 RF 전력은 전체 가용 RF 전력 중의 일부이며 모든 전력 증폭기가 각 개별 범에 기여한다. 하나의 HPA가 고장 시에도 일부 기능을 수행할 수 있다. 따라서, 가용한 전체 RF 전력을 크기가 작은 입력 신호를 조절함으로써 안테나 범들 사이에 아주 유연하게 할당 할 수 있다. 이러한 장점들은 향후 통신위성의 방향이라 할 수 있는 유연성 있는 설계에 매우 부합하는 특성이라 할 수 있다. 특히, 높은 데이터 속도의 요구와 주파수 포화로 인해 향후 주로 사용될 K-대역과 같이 고주파 영역에서 부품들의 편차로 인해 MPA의 적용의 어려움이 예상되는 바 이를 해결할 연구가 절실히 필요하다고 생각된다.

#### 제 3 절 다중 포트 증폭기 동작 원리

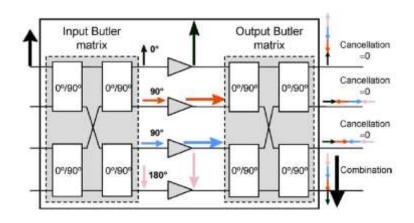

그림 1-5 4x4 다중포트 증폭기의 동작 원리[12, 14]

위 그림은 4x4 다중포트 증폭기의 블록도를 보여주고 있다. 이 구조는 2x2의 평형 증폭기를 확장한 구조로 이해할 수 있다. 위 그림에서 입력에서 들어오는 신호는 포트간 90도 위상 차이를 갖는 입력 버틀러 행렬을 통해 4개의 위상을 갖는 신호로 나누어진 후, 각각 개별 증폭기를 거친 다음 출력 버틀러 행렬을 통해 맨 밑의 포트에서 결합되고 있다.

그림 1-6 다중포트 증폭기의 단일 경로 동작

입출력 버틀러 행렬에서 어떻게 전력이 분배 결합되는지를 간략히 살펴보자. ICH1에 신호가 입력되면 모든 커플러가 90도 위상차를 가지고 있고 모든 증폭기의 증폭 이득이 완전히 동일하면 이상적으로는 OCH4에서만 신호가 출력되고나머지는 모두 상쇄된다.

$$OCH_4: \frac{1}{4}V_1 \times (-GA - GB - GC - GD) \neq 0$$

(출력 포트) (1-1)

$$OCH_1: \frac{1}{4}V_1 \times (GA - GB - GC + GD) = 0$$

(1-2)

$$OCH_2: \frac{1}{4}V_1 \times (-jGA + jGB - GC + GD) = 0$$

(1-3)

$$OCH_3: \frac{1}{4}V_1 \times (-jGA - jGB + jGC + jGD) = 0$$

(1-4)

기존 포트 별 개별 증폭기와 비교하여 다중포트 증폭기의 장점은 입력 신호를 분배하여 증폭하기 때문에 더 낮은 전력포화특성을 갖는 증폭기로 동일한 특성을 얻을 수 있다는 점이다. 다중포트 증폭기의 모든 입력 포트에 신호가 들어오는 경우에는 이상적으로 구성 증폭기에서 처리하는 신호 레벨은 단일 포트 증폭기와 동일하다. 따라서, 다중포트 증폭기의 모든 입력포트에 신호가 인가되는 상황을 제외하면 단일포트 증폭기에 비해 DC 전력소모가 적고, MPA 구성 증폭기가일반적으로 더 낮은 포화특성으로 동작하고 있다. 특히 출력 전력을 가변 하는 경우에 전력의 유연성을 높일 수 있는 장점을 가진다.

여기서 유의할 점은 버틀러 행렬과 증폭기 간의 부정합이 존재한다면 신호의 상쇄가 완전하지 않게 된다. 이 문제는 MPA를 실제 환경에 적용하는데 가장 큰 문제점으로 작용한다. 특히, 주파수가 높아지면 증폭기와 같은 능동소자뿐 아니라 수동소자 간 존재하는 부정합으로 인해 출력 포트 간의 높은 격리를 유지하기 어렵게 된다. 따라서, MPA 는 별도의 보정 회로를 요구한다.

$$n2 = |L1|e^{L1\theta} \tag{1-5}$$

$$n3 = |L2|e^{L2\theta} + |L1L3L4|e^{L1\theta + L3\theta + I4\theta}$$

(1-6)

$$n4 = n3 |L4| e^{L4\theta} + |L1L3| e^{L1\theta + L3\theta}$$

(1-7)

$$n5 = n2 |L5| e^{L5\theta} + n4 |L7L6| e^{L7\theta + L6\theta}$$

(1-8)

$$n6 = n5 |L6| e^{L6\theta} + n4 |L7| e^{L7\theta}$$

(1-9)

위의 수식들은 MPA 블록을 나타낸다. N은 노드, L은 전송 선로를 나타낸다.  $\parallel$  은 크기를 나타내며,  $\Theta$ 는 위상을 나타낸다.

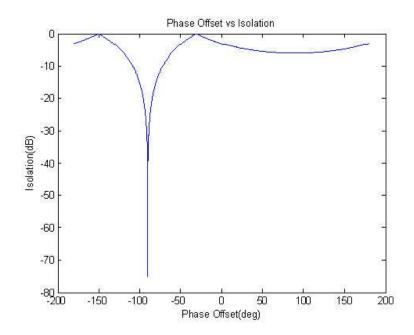

그림 1-7 위상 오프셋과 격리도 관계

경로에서 진폭의 변화가 없다고 가정하면 위상 오프셋에 따른 격리도 변화를 확인할 수 있다. 이전 그림에서 위상 오프셋이 -90도일 때가 가장 격리도가 높다. 나머지 위상 값에서는 격리도가 낮아짐을 확인할 수 있다.

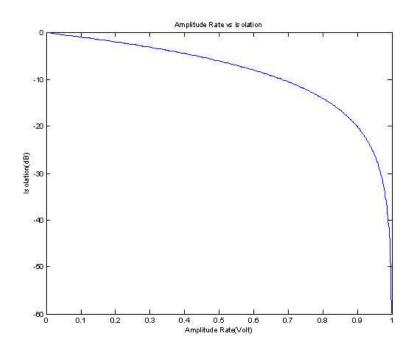

그림 1-8 진폭 비율과 격리도 관계

경로에서 위상이 이상적인 상황이라고 가정하면 진폭 비율에 따른 격리도 변화를 확인할 수 있다. 위의 그림에서 진폭 비율이 1일 때, 즉 진폭이 동일할 때 가장 큰 격리도를 보인다. 반면 진폭 비율이 낮아질수록 격리도가 낮아진다.

그림 1-9 IQ 오류의 예[15]

다중 증폭기에 QPSK 신호를 인가하여 출력 신호를 살펴보면 신호의 부정합 종류에 따라서 그림과 같은 IQ 오류가 발생한다. 이 때, 이를 구분하는 방법은 다음과 같다. 먼저, DC 오프셋의 경우 원점에서 점들까지의 유클리디안 거리가모두 다르다. 다음으로, 이득 불균형의 경우 한 점에 대한 절대값을 취한 경우 X나Y 좌표 값 중 한 가지가 더 큰 값을 가지게 된다. 끝으로, 위상 불균형의 경우 절대값을 취하지 않았을 때, 한 샘플에 대해 수평선과 수직선을 동시에 연결하더라도 만나는 점이 하나도 없다는 점으로 특성화 할 수 있다.

#### 제 4 절 기존 보정 방식의 예

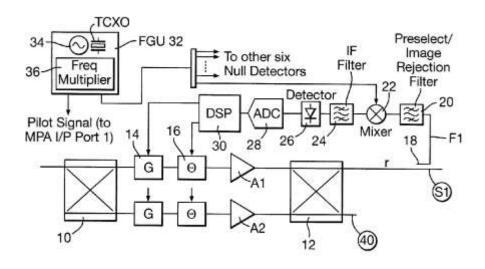

그림 1-10 기존 보정 방식의 예[16]

위 그림은 MPA의 포트 간 격리도를 높이기 위한 보정 방식의 전형적인 예를 보여주고 있다. 그림에서 출력포트인 S1에서 이상적으로는 신호가 발생되지 않아야 하지만 신호 경로의 부정합에 의해서 신호가 발생하게 된다. 이를 보상하기 위해 그림의 S1 노드에서 신호를 검출하고 기준 신호보다 작은 값이 검출되도록 14, 16의 위상과 진폭을 보정하는 방식이다.

이 방식은 IF 주파수 변경 후 검출하는 방식으로(헤테로다인 구조) 파일럿 신호가 신호 경로 상의 신호와 주파수가 달라서 부가적인 파일럿 신호 생성기가 요구된다. 또한, 검출된 신호 S1에서 나온 신호는 신호경로에서 위상 부정합이 발생했는지 진폭 부정합이 발생했는지 구분을 할 수가 없다. 검출기는 단지 신호 크기만 검출하기 때문이다. 따라서 신호 처리기에서 14, 16번을 순차적으로 두 개를 반복해서 최적점을 찾아야 하기 때문에 보정 시간이 상대적으로 길 수 있다. 이 보정 방식을 2x2에서 NxN으로 확장하게 되면 null 포인트(신호가 나오지 않는점)가 여러 곳 존재하게 되며, 이런 신호를 검출하기 위해서 검출기가 필요하나, 도파관과 같은 버틀러 행렬의 중간 노드에서 신호를 검출하기에 쉽지 않으며, 검출기 때문에 행렬의 대칭성을 유지하기 어려운 문제가 예상된다.

## 제 2 장 다중 포트 증폭기 출력 포트간 격리 향상을 위한 제안 구조

#### 제 1 절 제안하는 구조

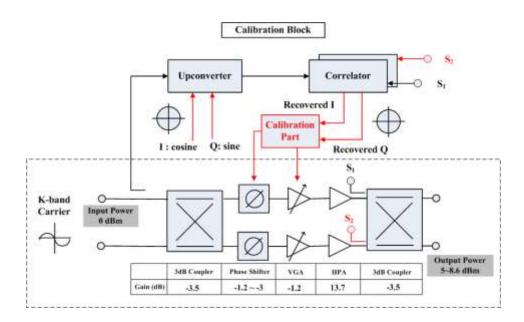

그림 2-1 제안하는 다중 포트 중폭기 출력 포트 간 격리 향상을 위한 구조 의 블록도

위 그림은 MPA의 출력 포트 간 격리도를 개선하기 위해 본 연구에서 제안하는 보정 알고리즘의 전체 블록도를 보여주고 있다. 제안하는 보정회로의 구조는 다중포트(multi-port) 복조기를 이용한 직접변환 방식이다. 기존의 믹서 방식의 직접변환 방식과 비교하여 다중포트 복조기의 장점은 낮은 RF와 LO 입력 신호에 동작하도록 설계된 점이다. 기존의 믹서를 이용한 직접변환 방식은 LO신호에 스위칭 방식의 동작을 하는데 비해 다중포트 직접 변환 방식은 스퀘어 법칙(square-

law) 영역 동작을 함으로써 낮은 입력 신호에서 동작할 수 있도록 최적화되어 있다.

위 그림에서 보이듯이 FPGA(Field Programmable Gate Array)에서 1MHz 베이스밴드 사인과 코사인 신호를 생성한다. 그 후 그림 2-1에서 보이듯이 RF 대역으로 상향변환(up-conversion)된다. 상관기 (correlator 또는 demodulator)는 상향 변환된 베이스밴드 신호와 MPA의 출력신호와의 상관관계를 측정한다.

보정 알고리즘은 FPGA 상에 디지털 로직으로 구현한다. 보정 알고리즘에서 I와 Q 채널에 해당 하는 RF 신호 경로의 위상 차이를 먼저 계산한다. 다음으로 진폭의 차이를 계산한다. 계산된 진폭과 위상 값에 따라 생성된 전압 값을 가변 위상 천이기와 감쇄기에 전달한다. 이상적인 진폭과 위상을 찾을 때까지 위상과 진폭을 지속적으로 피드백 받고 위상천이기와 감쇄기의 전압 값을 조정하여 이상적인 위상과 진폭을 찾게 된다. 최종적으로 이상적인 진폭과 위상을 찾은 경우 다중 포트 증폭기(Multiport Amplifier, MPA)의 포트간 격리도가 최대가 된다.

#### 제 2 절 검증용 UHF 대역 다중 포트 증폭기 블록

그림 2-3 검증을 위한 MPA 구조 블록도

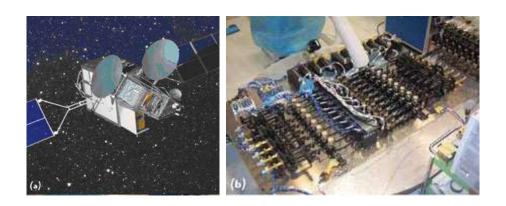

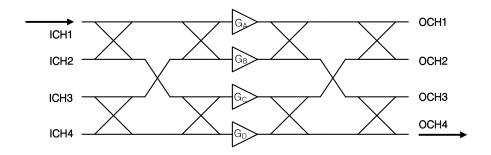

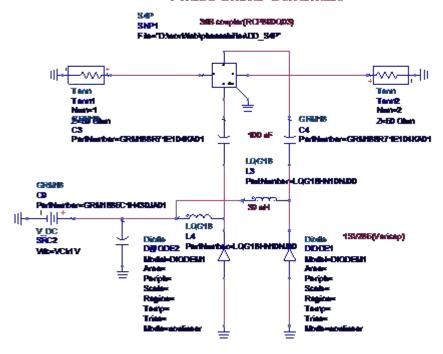

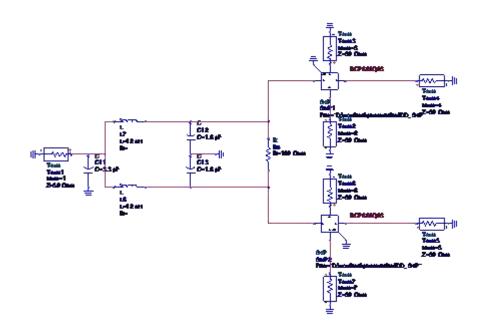

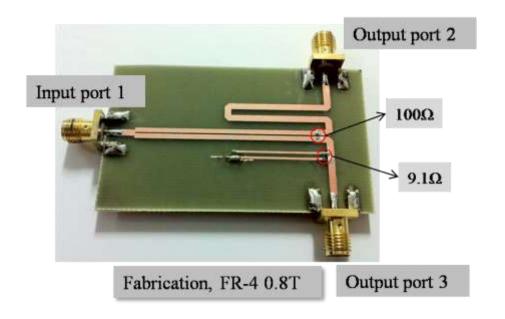

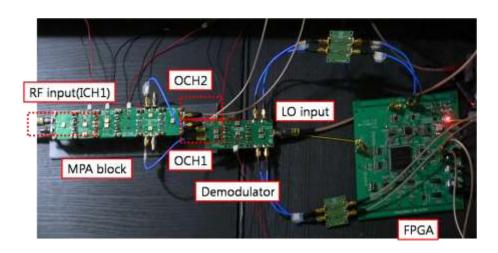

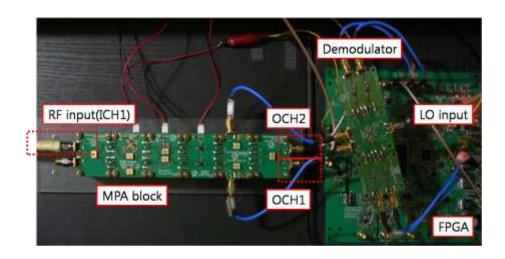

본 연구에서는 MPA 블록의 기본 단위라고 할 수 있는 그림 2-3의 2x2 증폭기를 이용하여 제안한 보정 알고리즘 검증하였다. 그림에서 3-dB 커플러는 입출력 단의 버틀러 행렬을 생성하는데 이용한다. 이상적으로 ICH1에 신호가 입력되면 OCH1로, ICH2에 입력되면 OCH2에서 출력된다. 알고리즘의 검증을 쉽게 하기 위해서 상단신호 경로에는 가변 위상 천이기와 감쇄기를 구현한다. 하단 신호 경로에는 고정위상 천이기와 감쇄기를 구현한다. 한단신호 경폭된 신호는 10-dB커플러를 통과한다. 커플링 된 신호는 복조기로 전달된다. 또한 원래의 신호는 출력단 3-dB 커플러를 통해서 출력되게 된다. 다음은 실제 제작한 검증용 MPA블록의 사진이다.

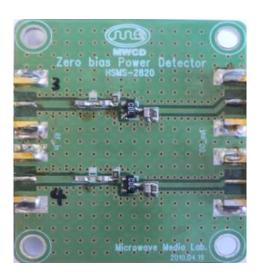

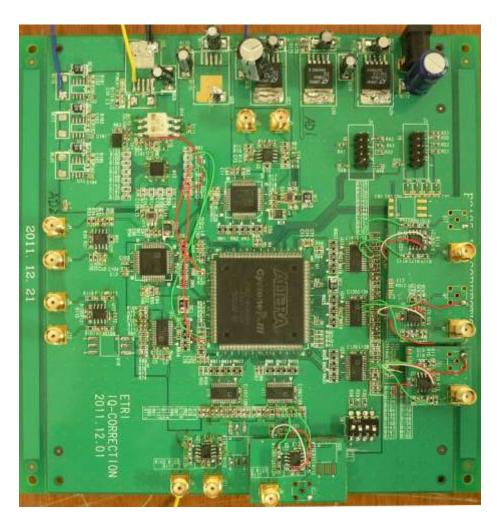

그림 2-4 검증용 UHF 대역 MPA 블록

동일한 크기의 너비와 높이를 가지도록 각 세부 블록 별로 구현을 했다. 이는 고장이 발생했을 때 필요한 블록만 수정하기 용이하게 하기 위함이다. 상단의 전선은 FPGA의 DAC 버퍼로 연결되는 가변 위상 천이기와 가변 감쇄기를 연결하는 전선과 전력 증폭기의 바이어스 전압을 연결하는 전선으로 이뤄져 있다.

#### 제 3 절 검증용 UHF 대역 7-포트 복조기 블록

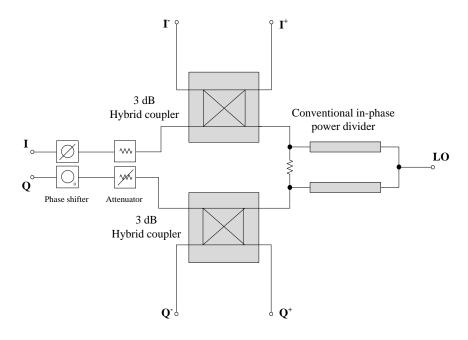

그림 2-5 검증용 UHF 대역 7-포트 복조기 블록도

위 그림은 7-포트 복조기를 보인다. 7-포트 복조기는 잘 알려진 6-포트 블록에서 LO 입력 신호를 0도와 90도로 분배하는 하이브리드 커플러를 생략하고 직접 I와 Q 신호를 인가하는 구조다. 여기서 MPA 블록의 10-dB 커플러를 통과한 916MHz의 LO 신호는 각각 I와 Q의 신호로 인가된다. RF신호는 LO신호보다 1MHz 더 큰 주파수를 인가한다. 이는 상측(upper sideband) SSB신호를 가정하는 것이다. RF와 LO가 덧셈 혼합(additive mixing)되면 I+, I-, Q+, Q-의 신호가 발생한다. 위상천이기는 정확한 90도일 때 전압 값으로 고정한다. 감쇄기는 I와 Q 채널 신호의 파워가 동일할 때 전압 값으로 고정한다.

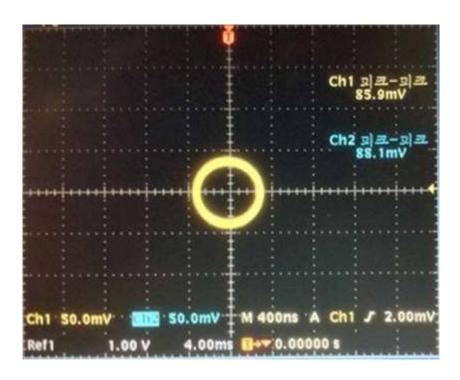

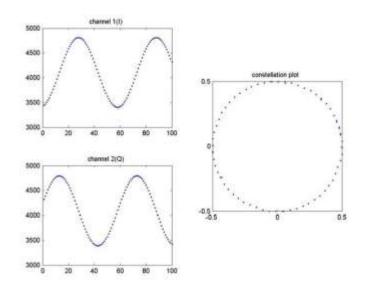

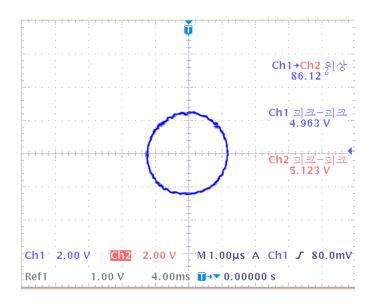

그림 2-6 조정된 복조기의 성상도

본 연구에서는 기존 7-포트 복조기에 능동과 수동 소자의 제작 편차를 고려할 수 있도록 LO신호 쪽에 가변 위상기와 감쇄기를 포함하고 있다. 복조기에 이상적인 I-Q 신호가 인가되고 검출기의 신호를 오실로스코프를 이용하여 리사주(Lissajous) 파형을 관측하면 정확하게 원이 그려져야 한다. 하지만 90도 하이브리드와 검출기의 부정합 등의 이유로 실제 복조기의 리사주 파형은 원이 아닌 타원형이 그려질 수 있다. 이러한 경우 가변 위상기와 감쇄기를 조정하여 리사주 파형을 원이 되도록 조정하여 준다.

고정형 복조기의 경우 FPGA 알고리즘에서 위상 오차 값을 조정하여 최적위상을 찾을 수 있도록 조정한다. 현재의 고정형 복조기 구현에서는 디지털오프셋 변경을 위해서 다시 합성을 해야 한다. 만약, 여분의 핀이 있다면 고정 소수점 형숫자를 입력 받을 수 있도록 하여 외부에서 조정할 수 있도록 할 수 있다. 이는

실제 동작 중의 온도 변화 등으로 인한 복조기의 편차를 실시간으로 고려할 수 있는 장점이 있다. 다음은 제작한 보정 가능한 7-포트 복조기의 회로 사진이다.

그림 2-7 제작한 검증용 UHF 대역 7-포트 복조기

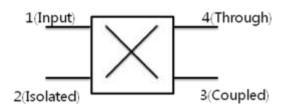

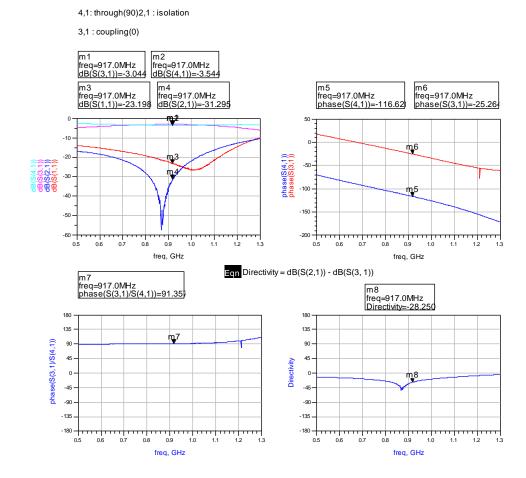

### 제 4 절 3-dB 커플러

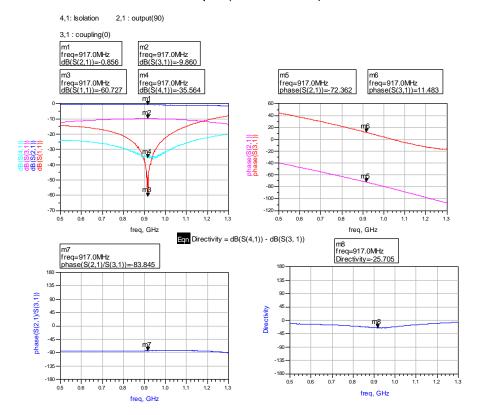

검증 모듈에서 사용된 쿼드러쳐 특성을 갖는 3-dB 커플러로 RN2 社 의 RCP890Q03를 사용하였다. 중심 주파수는 917 MHz이고, 측정한 전달, 격리, 반사, 지향도(directivity), 진폭과 위상의 평형 특성은 다음의 그림 2-10과 같다.

그림 2-8 3-dB 커플러의 포트 기능

그림 2-9 RCP890Q03 커플러

### 3 dB Coupler(RCP890Q03) @ 917 MHz

그림 2-10 3-dB 커플러의 S-파라미터 (b) 3-dB 커플러의 위상 (c) 위상 오류 (d) 지향도

결합포트와 Thru포트에서 위상 차는 91.357도, 진폭 편차는 0.5dB, 지향도(directivity)는 28.25dB의 측정되었다.

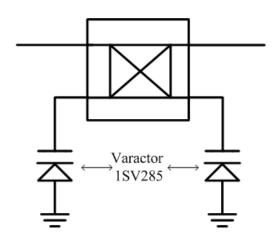

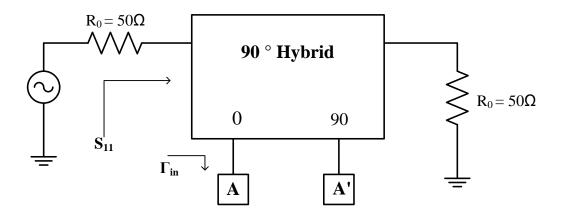

## 제 5 절 위상 천이기

그림 2-11 전압 가변형 위상 천이기 블록도

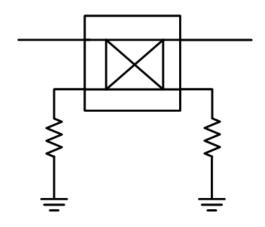

먼저 가변형 위상 천이기를 살펴본다. 블록도를 보면 90도 커플러의 through와 coupled 포트에 연결된 소자는 동일한 소자이다. 그러므로 특성이 거의 동일하며 우수한 반사손실 특성을 나타낸다. 또한, 대칭적인 구조 덕분에 S11과 S22가 거의 유사한 값을 가진다[17].

### Phase Shifter Schematic

그림 2-12 전압 가변형 위상 천이기 회로도

그림 2-13 전압 가변형 위상 천이기 위상 계산을 위한 블록도[17]

바이어스 인덕터와 기생 소자를 포함한 부하의 입력 임피던스는 다음과 같다.

$$Z_{in} = \frac{\omega^2 C_f^2 C_v^2 (L + R_s) + j\omega L^2 C_f C_v (C_f + C_v) + R_s L^2 (C_f + C_v)^2}{\omega^2 C_f^2 C_v^2 + L^2 (C_f + C_v)^2}$$

(2-1)

부하의 반사 계수  $\Gamma_{in}=\left|\Gamma_{in}\right|e^{\theta}=rac{Z_{in}-Z_{o}}{Z_{in}+Z_{o}}$  이므로 위상은 다음과 같이 계산될 수 있다.

$$\theta = \tan^{-1} \left[ \frac{L(Z_o - R_s)(C_f + C_v)}{\omega C_f C_v (L + R_s - Z_o)} \right] - \tan^{-1} \left[ \frac{-L(Z_o + R_s)(C_f + C_v)}{\omega C_f C_v (L + R_s + Z_o)} \right]$$

(2-2)

이 때, Cf는 고정 캐패시터의 캐패시턴스, Cv는 바랙터 다이오드의 캐패시턴스이다. 동작은 가변 캐패시턴스의 값이 변하면서 위상 특성이 바뀌는 것이다.

그림 2-14 전압 변화에 따른 위상 천이(deg)

제작한 위상 천이기는 전압에 따른 감쇄 변화는 0.27dB, 위상 변화는 96.02도다. 전압이 0V 일 때, -1.04 dB로 가장 적은 감쇄 값을 가진다. 전압은 최대 5V까지 가변된다.

그림 2-15 고정형 위상 천이기

반면, 고정형 위상천이기는 고정된 값의 캐패시턴스를 연결하여 특정 위상 값을 가지도록 한다.

그림 2-16 제작한 가변형 및 고정형 위상 천이기

부하의 입력 임피던스는 다음과 같다.

$$Z_{in} = \frac{1}{j\omega C_f} \tag{2-3}$$

위상을 계산하면 다음과 같다.

$$\theta = \tan^{-1} \left[ \frac{1}{Z_o \omega C} \right] - \tan^{-1} \left[ \frac{-1}{Z_o \omega C} \right]$$

(2-4)

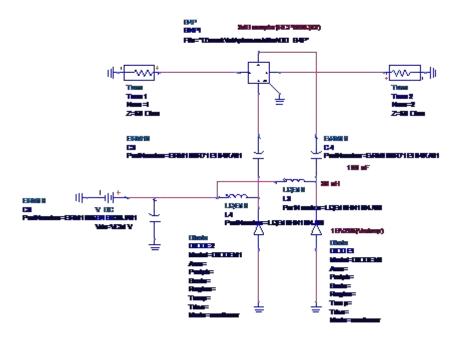

## 제 6 절 감쇄기

그림 2-17 가변형 감쇄기

가변형 위상 천이기와 구조면에서 유사하나, 바랙터 다이오드 대신 핀다이오드가 사용된다. 핀 다이오드의 저항 성분이 변화함에 따라서 감쇄 특성이바뀐다. 다만, 이 때, 위상도 바뀌게 되며 핀 다이오드의 기생 성분을 보상함으로써위상 변화를 최소화한다.

#### Phase Shifter Schematic

그림 2-18 전압 가변형 감쇄기 회로도

입력 임피던스는 다음과 같다.

$$Z_{in} = R_s + \frac{R_j}{1 + j\omega R_j C_j} + j\left(\omega L_s - \frac{1}{j\omega C_f}\right)$$

(2-5)

반사 계수  $\Gamma_{in} = \left|\Gamma_{in}\right| e^{\theta} = \frac{Z_{in} - Z_o}{Z_{in} + Z_o}$  이므로 위상은 다음과 같이 계산될 수 있다.

$$\theta = \tan^{-1} \left[ \frac{\omega L_{s} - \frac{\omega R_{j}^{2} C_{j}}{1 + \omega^{2} R_{j}^{2} C_{j}} - \frac{1}{\omega C_{f}}}{R_{s} - Z_{o} + \frac{R_{j}}{1 + \omega^{2} R_{j}^{2} C_{j}^{2}}} \right] - \tan^{-1} \left[ \frac{\omega L_{s} - \frac{\omega R_{j}^{2} C_{j}}{1 + \omega^{2} R_{j}^{2} C_{j}} - \frac{1}{\omega C_{f}}}{R_{s} + Z_{o} + \frac{R_{j}}{1 + \omega^{2} R_{j}^{2} C_{j}^{2}}} \right]$$

(2-6)

그림 2-19 전압 변화에 따른 감쇄(dB)

제작한 감쇄기의 전압에 따른 감쇄 변화는 0.27dB, 위상 변화는 0.6도이다. 전압이 0V 일 때, -1.17dB로 가장 적은 감쇄 값을 가지며 0.5V일 때 -3.1dB의 값을 가진다.

그림 2-20 고정형 감쇄기 블록도

그림 2-21 제작한 가변형 및 고정형 위상 천이기

## 제 7 절 전력 증폭기

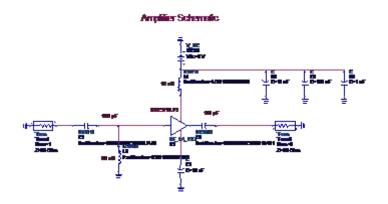

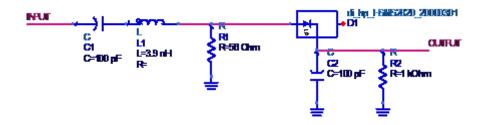

그림 2-22 전력 증폭기 회로도

검증용 MPA 모듈에 사용된 증폭기는 Hittite社의 HMC372LP3로 구현하였다. 5V 바이어스 전압에 대해 118mA의 DC 전류가 흐르며, RF 이득은 13.7dB이다. 1dB 입력 IP는 8.3dBm이다. 아래는 제작한 전력 증폭기의 사진이다.

그림 2-23 제작한 전력 증폭기

## 제 8 절 출력 결합을 위한 10-dB 커플러

그림 2-24 10-dB 커플러

그림 2-24는 사용한 10-dB 커플러의 포트 위치를 표시하고 있다

그림 2-25 제작한 10-dB 커플러

### 10 dB Coupler(RCP890Q10) @ 917 MHz

그림 2-26 (a) 10-dB 커플러의 S-파라미터 (b) 10-dB 커플러의 위상 (c) 위상 오류 (d) 지향도

측정한 10-dB 커플러의 두 포트간 위상차는 93.845도, 크기는 9.01dB 차이가 나며 지향도(directivity)는 28.25dB다. 이 때, 입력에서 출력으로 전달되는 값은 -0.856dB이며, 복조기로 전달되는 값은 -9.86dB이다.

### 제 9 절 7-포트 상관기

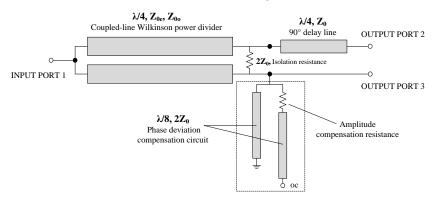

그림 2-27 복조를 위한 7-포트 상관기 구조

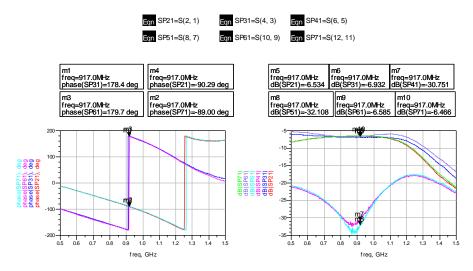

위 그림은 복조를 위해 사용한 7-포트 상관기의 구조를 보여주고 있다. 왼쪽부분은 집중소자로 구현한 윌킨슨 전력 분배기의 구조다. 뒷 단은 90도 커플러를 2개 연결했다. 1번 포트로 916MHz RF신호를 입력한다. 4번과 5번 포트에 10-dB 커플러로 부터 917MHz LO신호가 입력된다. 포트 2, 3과 포트 6, 7은 LO와 RF 신호가 혼합되어 복조기로 전달된다.

#### 7 Port Correlator S Parameter @ 917 MHz

그림 2-28(a) 7-포트 상관기 위상 측정(b) 7-포트 상관기 크기 측정

4번과 5번 RF신호 입력 포트는 LO신호에 대해 30dB 정도의 격리도를 보인다. 포트 별 전달되는 신호의 크기 편차는 최대 0.466dB이다. 위상 편차는 각각 1.31도, 1.3도 이다.

### 제 10 절 정밀 I-Q 전력 분배기

#### "PRECISE I/Q DIVIDER"

그림 2-29 정밀한 I-O 신호 분배기

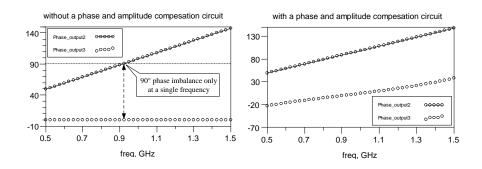

그림 2-30(a) 보상하기 전의 위상 차이(b) 보상 후의 위상 차이

앞서 소개한 7-포트 상관기는 이상적이지 못한 수동소자들과 검출기들의 제작 편차로 인해 보정이 필요하다. 보정하기 위해서는 LO포트에 정확한 I-Q 신호를 인가해야 한다. 이를 위해 그림 2-29와 같은 정밀한 I-Q 신호 분배기가 필요하다. 위상과 진폭을 보상하는 회로가 있기 전에는 그림 2-30의 (a)에 있는 것처럼 정확히 90도 위상 차는 중심 주파수에서만 이루어진다. 그러므로 위상 편차 보상회로는 병렬 단락과 개방 스텁의 조합으로 만들어진다. 이들 각각의 병렬 스텁은인덕터와 캐패시터로 표현될 수 있다. 이 회로가 추가되면 90도 위상 차를 가지는주파수 대역이 확장된다. 보상 회로는 중심 주파수에서 공진되어 입력 임피던스가무한대가 된다. 또한 90도 위상 지연을 위한 전송 선로의 감쇄로 인한 출력단의신호 크기의 편차를 보상하기 위해서 다른 쪽 경로에 저항을 이용하여 보상하였다.

그림 2-31 제작한 정밀 전력 분배기

그림 2-31은 제작한 정밀한 전력 분배기를 보인다. 유전율 4.5인 FR-4에 제작했다. 도체는 0.8T 두께이다. 손실 탄젠트 0.02이다.

그림 2-32 전력 분배기의 반사 손실과 격리도 (b) 위상과 크기 차이

제작한 정밀 I-Q 신호 분배기의 중심 주파수는 916MHz, 측정된 반사 손실은 23.38dB, 격리도는 31.54dB이다. 크기 편차는 0.009dB이고, 위상 편차는 90.087도이다.

### 제 11 절 전력 검출기

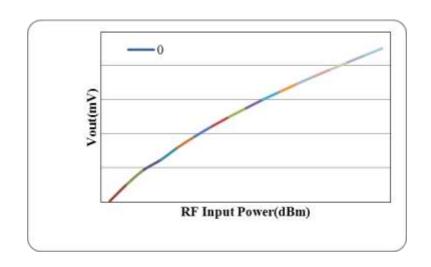

그림 2-33 전력 검출기 회로도

전력 검출기는 7-포트 복조기에서 LO와 RF 신호를 덧셈 혼합한 신호의 크기를 검출한다. 즉, 검출기에 이용된 다이오드 특성을 이용하여 하향 직접 변환을 수행하는 부분이다.

그림 2-34 RF 입력 전압 비 출력 전압

제작한 특성을 보면 917MHz에서 0~16dBm을 입력했을 때, 수 mV의 출력을

가지기 때문에 ADC 입력 전에 증폭해 주어야 한다. 아래는 실제 제작한 회로이다.

그림 2-35 제작한 전력 검출기

코사인 파형을 가지는 RF 신호의 주파수를  $\omega_{RF}$  라고 하고, 국부 발진단의 주파수를  $\omega_{LO}$ 라고 하면 신호는 다음과 같이 표현된다[20].

$$v_{RF}(t) = V_{RF} \cos \omega_{RF} t$$

$$v_{LO}(t) = V_{LO} \cos \omega_{LO} t$$

(2-7)

다이오드 전류 공식은 다음과 같다.

$$I(V) = I_s(e^{\alpha V} - 1)$$

(2-8)

$$\alpha = \frac{q}{nkT} \tag{2-9}$$

q는 전자의 전하량, k는 Boltzmann 상수, T는 온도 n은 이상계수(ideality factor), Is는 포화 전류이다. Is의 일반적인 값은  $10^{-6} \sim 10^{-15} \rm A$  정도이고,  $\alpha$ 는 T=290K에서 약  $\frac{1}{25mV}$  이다.

$R_j$  를 다이오드의 접합 저항이라고 할 때, 식 (2-8)의 Taylor 급수 근사 공식으로부터  $G_d=rac{1}{R_j}$ 이고 이 값이 (2-8) 수식의 1차 도함수 값 임을 알 수 있다. 그래서 근사 공식은 최종적으로 다음과 같다.

$$I(V) = I_0 + vG_d + \frac{v^2}{2}G'_d + \dots$$

(2-10)

전력 검출기의 입력 단으로는 916MHz의 LO신호와 917MHz의 L/Q RF신호가 입력되므로 (2-10)의 근사 공식에서 v는 (2-7)의 합으로 표현될 수 있다.

$$i(t) = I_0 + G_d[v_{RF}(t) + v_{LO}(t)] + \frac{G'_d}{2}[v_{RF}(t) + v_{LO}(t)]^2 + \dots$$

(2-11)

3차 항은 다음과 같이 계산된다.

$$i(t) = \dots + \frac{G'_d}{4} [V_{RF}^2 (1 + \cos 2\omega_{RF} t) + V_{LO}^2 (1 + \cos 2\omega_{LO} t) + 2V_{RF} V_{LO} \cos(\omega_{RF} - \omega_{LO}) t + 2V_{RF} V_{LO} \cos(\omega_{RF} + \omega_{LO}) t]$$

(2-12)

즉, DC 항을 제외하면 합, 차 항만 남게 된다. 그래서 1MHz 신호가 검출되게 된다.

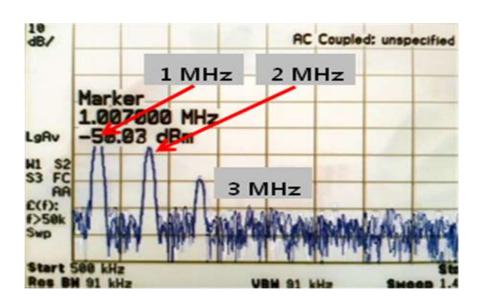

그림 2-36 하모닉 성분의 발생

실제로 측정하면 1MHz 신호만 있는 것이 아니라 상호 변조로 인한 하모닉성분까지 생성된다. 하모닉의 제거를 위해 1MHz 대역 통과 필터를 구현한다.

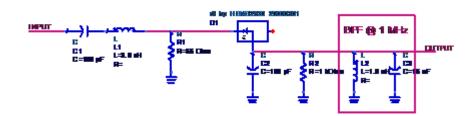

그림 2-37 최종 전력 검출기 회로도

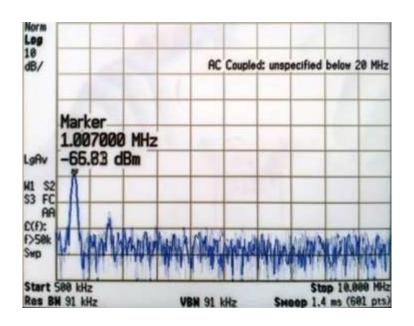

아래는 최종적으로 고차 하모닉을 제거한 결과를 측정한 것이다.

그림 2-38 하모닉이 제거된 신호

## 제 12 절 수동 보정 측정 결과

그림 2-39 위상 천이기 전압 가변시 MPA 출력 전력

MPA 블록의 위상 천이기의 전압 값을 조정하면 그 중 가장 큰 격리도를 가지는 전압 값이 존재한다. 최대한의 격리도는 입력 전압 간격의 세밀도에 따라 더 커질 수 있다. 실험 결과 전압이 2.9V일 때, 최대 24.88dB의 격리도를 얻었다.

그림 2-40 감쇄기 전압 가변시 MPA 출력 전력

위상 천이기와 마찬가지로 감쇄기의 전압 값을 조정하면 최대한의 격리도를 얻는 전압 값을 알 수 있다. 다만, 감쇄가 너무 크면 출력 신호 자체가 감소해 버리기 때문에 최대 격리도를 얻은 전압 값 이상에서는 격리도가 다시 감소하기 시작한다. 위상 천이기의 전압을 2.9V로 고정하고, 감쇄기의 전압을 0.46V 로 했을때 56.08 dB의 격리도를 얻었다.

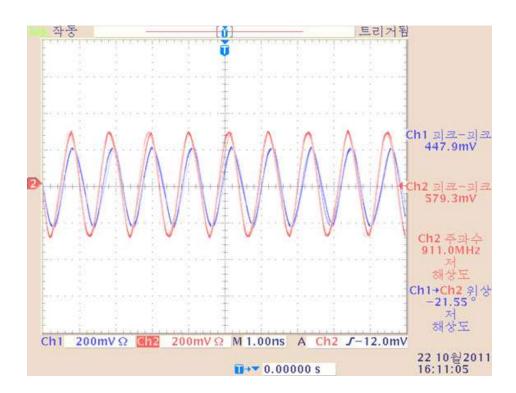

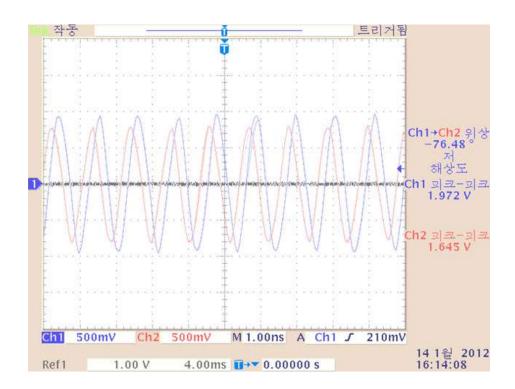

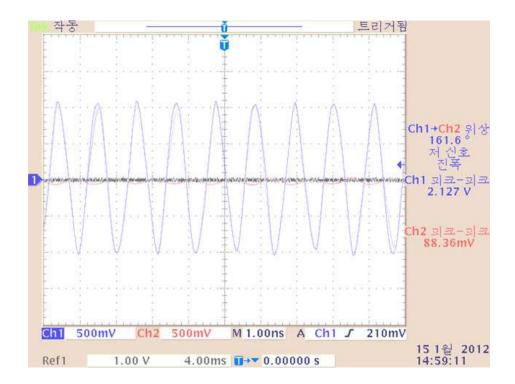

그림 2-41 수동 보정 전 MPA 출력 파형

위의 그림은 수동 보정을 하기 전 시간 도메인에서의 MPA 출력 파형을 보인다. 이 때 7-포트 상관기에 있는 감쇄기의 전압 값은 0.4V에 고정되어 있다.

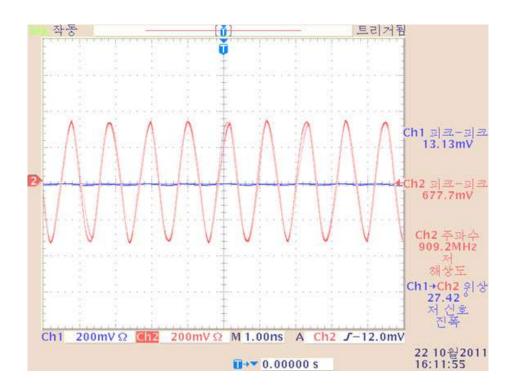

그림 2-42 수동 보정 후 MPA 출력 파형

위의 그림은 수동 보정한 후 시간 도메인에서 MPA 출력 파형을 보인다. OCH1의 신호가 OCH2에 비해서 가시적으로 매우 적음을 확인할 수 있다. 즉, 보정 전에는 격리도가 낮았지만, 보정 후에는 격리도가 높아짐을 확인할 수 있다. 알고리즘은 이러한 수동 보정 과정을 자동화 하는 과정을 설명한다.

# 제 3 장 격리도 향상 보정 알고리즘 FPGA 회로

## 제 1 절 FPGA 보드

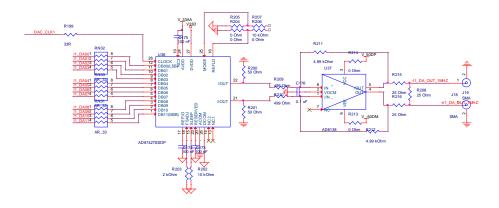

그림 3-1 IQ 보정 FPGA 보드 회로도

그림 3-2 제작한 IQ 보정을 위한 FPGA 보드

위 그림은 최종적으로 제작된 IQ 보정을 위한 FPGA 보드를 보인다.

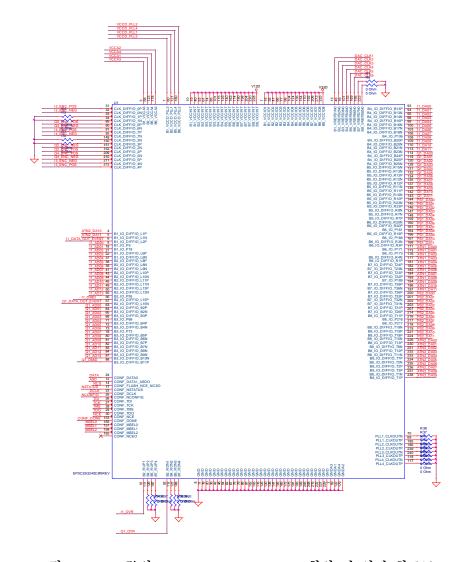

그림 3-3 Altera社의 EP3C25Q240C8N FPGA 칩의 핀 연결 회로도

사용한 FPGA 보드는 Altera社의 Cyclone III EP3C25Q240C8N이다. 가용 자원으로 24,624개의 로직 엘레멘츠와 66개의 M9K 메모리 블록, 608,256비트의 메모리, 66개의 18X18 곱셈기,4개의 PLL, 최대 215개의 사용자 IO가 있다.

## 제 2 절 활성 직렬 프로그래밍 방식

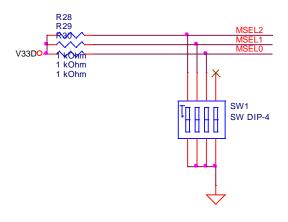

그림 3-4 MSEL의 선택을 통한 프로그래밍 모드 선택

MSEL을 DIP 스위치로 조절하여 어떠한 프로그래밍 방식을 이용할지 선택할 수 있다.

표 3-1 프로그래밍 설정 방식

| 설정 방식                  | MSEL | MSEL | MSEL | 설정 전압       |

|------------------------|------|------|------|-------------|

| (현경 경기<br>             | [2]  | [1]  | [0]  | 표준(V)       |

| 빠른 활성 시리얼 표준 (AS       | 0    | 1    | 0    | 3.3         |

| Standard POR)          |      |      |      |             |

| 빠른 활성 시리얼 표준 (AS       | 0    | 1    | 1    | 2.0/2.5     |

| Standard POR)          | 0    | 1    | 1    | 3.0/2.5     |

| 빠른 활성 시리얼 고속 (AS Fast  | 1    | 0    | 1    | 3.3         |

| POR)                   | 1    | U    | 1    | 3.3         |

| 수동 시리얼 표준(PS Standard  | 0    | 0    | 0    | 3.3/3.0/2.5 |

| POR)                   | · ·  | O .  | U    | 3.3/3.0/2.3 |

| 수동 시리얼 고속(PS Fast POR) | 1    | 0    | 0    | 3.3/3.0/2.5 |

| 빠른 수동 패러럴 고속 (FPP Fast | 1    | 1    | 0    | 3.3/3.0/2.5 |

| POR)                   | 1    | 1    | 0    | 3.3/3.0/2.3 |

| 빠른 수동 패러럴 고속 (FPP Fast | 1    | 1    | 1    | 1.8/1.5     |

| POR)                   | 1    | 1    | 1    | 1.0/1.3     |

현재 보드는 빠른 활성 시리얼 고속 방식으로 설정한다. JTAG 방식이 이용되면 MSEL의 설정은 무시된다.

### 표 3-2 주요 설정 핀 설명

| 핀 이름           | 핀 설명                                  |

|----------------|---------------------------------------|

| DATA0          | 설정 데이터의 입력 핀으로 Active Serial 방식으로 이용  |

|                | 한다.                                   |

| MSEL[30]       | 프로그래밍할 때 설정 방법의 종류를 선택하는데 이용된         |

|                | 다.                                    |

| nCE            | LOW 상태일 때 장치가 이용가능 하다.                |

| nCONFIG        | 사용자 모드에서 LOW가 되면 이전 프로그램이 제거될         |

|                | 수 있으며 LOW에서 다시 HIGH 상태가 되면 다시 다운      |

|                | 로딩을 수행한다.                             |

| CONF_DONE      | 다운로딩 전과 하는 동안에 LOW로 되고 모든 데이터를        |

|                | 수신한 후에 HIGH가 된다.                      |

| nSTATUS        | 에러가 발생하면 LOW가 된다.                     |

| TCK            | JTAG의 클럭.                             |

| TMS            | JTAG의 TMS 핀                           |

| TDI            | JTAG의 입력 데이터                          |

| TDO            | JTAG으로의 출력 데이터                        |

| DCLK           | 설정을 위한 클럭                             |

| Flash_nCE_nCSO | Active Serial 모드에서 nCSO로 동작하며, 설정 장치가 |

|                | enable되도록 한다.                         |

| DATA1_ASDO     | 데이터 입력으로 사용된다.                        |

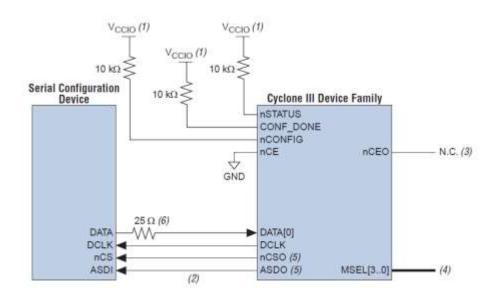

그림 3-5 단일 장치 활성 시리얼 설정 방식의 블록도

ASDO와 ASDI는 설정 장치를 제어하는 신호이다. nStatus, CONF\_DONE, nConfig핀에 10kOhm의 풀업 저항을 연결한다. DATA[0] 핀에 연결된 직렬 저항은 보드 상의 선로와 드라이브의 임피던스 부정합을 최소화한다. 또한, 이는 DATA[0]에 나타나는 오버슈트 현상을 줄인다.

AS 설정 방식에서, 직렬 설정 장치는 DCLK의 상승 에지에서 입력과 제어 신호를 가져오고 하강 에지에서 내보낸다. 이 동안 FPGA 보드는 DCLK의 하강 에지에 DCLK의 제어신호와 설정 데이터를 동시에 내보내고 가져온다. 설정하는 동안 nCSO는 LOW 상태에 있게 된다. DATA[1] 편으로는 DCLK에 따라서 제어 명령과 읽어야 하는 주소를 직렬 설정 장치로 보낸다. 설정 장치는 데이터를 DATA 핀에 제공한다. 설정이 완료되면 CONF\_DONE이 HIGH로 되어 초기화 준비가 완료된다. 또한 설정 핀들인 DATA[1.0], DCLK, nCSO는 HIGH 상태가 된다.

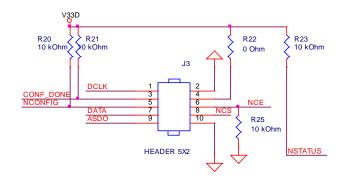

그림 3-6 단일 장치 활성 직렬 설정 방식 회로도

ISP(In system programmer)를 연결하기 위한 회로도 이다.

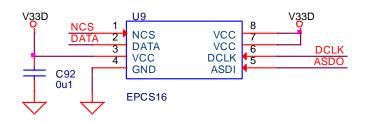

그림 3-7 코드를 저장하기 위한 PROM

EPCS16은 16,777,216 비트의 크기를 가진 PROM으로 프로그래밍 코드가 저장된다.

# 제 3 절 JTAG 프로그래밍 방식 설명

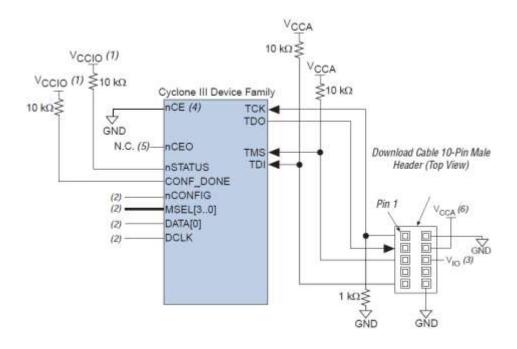

그림 3-8 JTAG 설정 방식의 블록도

TDI(Test Data Input)는 테스트를 위한 명령과 프로그래밍 데이터를 위한 직렬 입력편이다. 데이터는 TCK의 상승 에지 동안에 쉬프트 된다. TDO(Test Data Output) TDI와 동일한 데이터를 다루나 데이터 방향이 반대이다. TMS(Test Mode Select)는 TAP(Test Access Port) 제어기의 상태 머신의 전이를 결정하는 제어 신호를 제공한다. TCK(Test Clock Input)는 BST(Boundary-Scan Testing) 회로의 클럭이다.

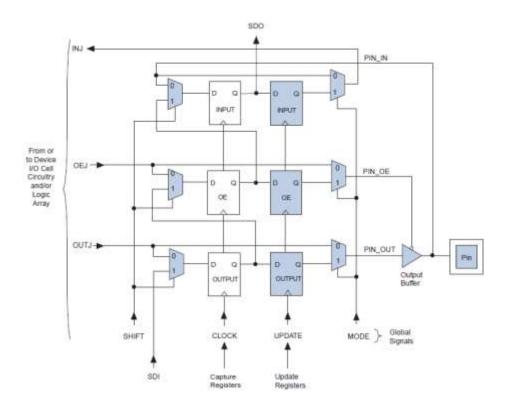

그림 3-9 IEEE 1149.1 BST 회로(EPC16)[18]

위의 회로는 JTAG의 IEEE 1149.1 표준인 BST(Boundary State Testing) 명령의 연산이 동작할 때 이용되는 회로이다. 여기에는 SAMPLE/PRELOAD, EXTEST, BYPASS, IDCODE, USERCODE, CLAMP, HIGHZ 등의 명령이 있다.

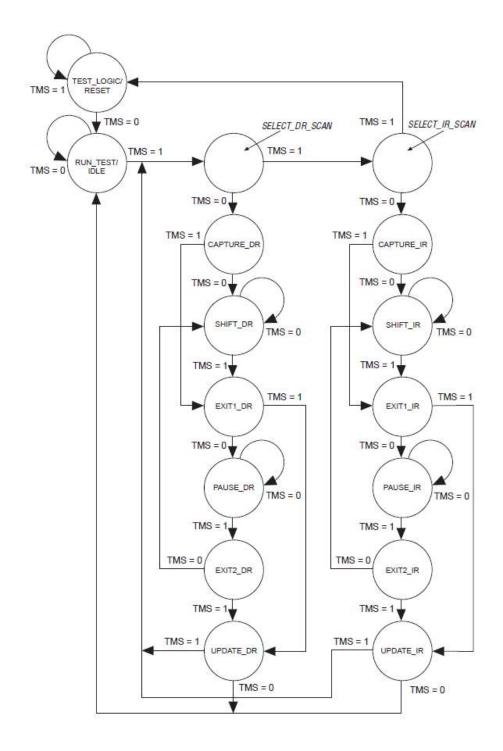

그림 3-10 IEEE 1149.1 BST 회로의 상태 머신도[18]

위 그림은 BST 희로의 16개의 상태를 가진 상태도를 보인다. TCK에 따라서 클럭킹되고 TMS 핀으로 제어된다.

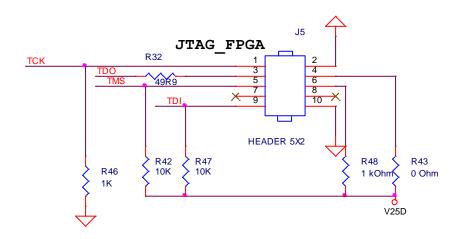

그림 3-11 JTAG 설정 방식의 회로도

위 그림은 ISP를 JTAG 모드로 동작시킬 때의 연결을 보이는 회로도다.

### 제 4 절 ADC 입력 드라이버

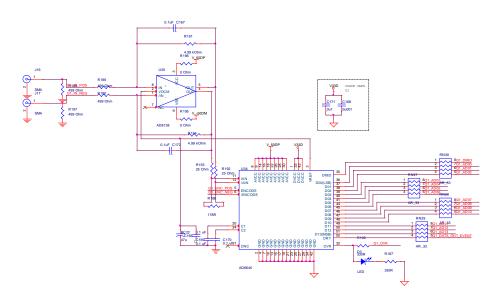

그림 3-12 ADC 입력 드라이버

위 그림에서 AD8138은 차동-차동 이득 블록으로 입력 신호를 증폭, 오프셋이동한다[19]. 모든 고속 ADC는 사용자에 의해 제공되는 샘플링 클럭의 특성에 매우 민감하다. Track/Hold 회로는 기본적으로 믹서이기 때문에 클럭에서 발생하는 노이즈, 왜곡, 타이밍 지터는 원하는 신호와 섞여서 ADC의 출력에 나타나게 된다. 그러므로 클럭의 입력부 회로와 클럭 소스에 대하여 매우 세심한 주의를 기울여야한다. 최대의 성능을 얻기 위해서는 클럭 소스는 반드시 차동 모드로 입력해야한다. 가장 좋은 신호원은 순수한 사인파를 생성하는 크리스털 오실레이터이다. ADC의 이론적으로 완벽한 신호 재생성 능력에 대한 편차를 왜곡(distortion)이라고하며 다음의 왜곡이 발생할 수 있다[23].

- 앨리어싱(Aliasing): 입력 샘플링 신호의 대역폭이 실제로는 제한되어 있지 않기 때문에 생기는 왜곡이다. 더 자세히 말하면, 실제 신호에는 나이퀴 스트 주파수 보다 높은 주파수 성분과 낮은 주파수 성분들이 혼재되어 있다. 앨리어스 주파수는 입력 신호의 주파수가 가지고 있는 여러 샘플링 속도의 가장 근사치 정수 값에서 입력 주파수 값을 뺀 것의 절대값으로 나타난다. 예를 들어, 2kHz 신호를 1.5kHz로 샘플링하면 500 Hz처럼 복원된다. 실제 신호에서 나이 퀴스트 주파수 주파수보다 높은 성분들은 왜곡된 샘플링 데이터를 생성하게 된다. 앨리어싱을 방지하기 위해서는 신호의 최고 주파수 성분의 약 5~10배 높게 설정해야 하며, 앨리어스 방지 필터가 ADC 이전에 사용되어야 한다. 만약 오버샘플링 컨버터인 시그마 델타 ADC를 이용한다면, 앨리어싱 방지 필터의 성능 요건을 낮출 수 있다.

- 어퍼쳐 효과(Integration/aperture effect): 샘플링 영역에서 샘플링하는 시점의특정 신호 값을 샘플로 획득하는 것이 아니라 시간 평균에 의해서 얻은 값을 샘플로 획득하기 때문에 생기는 현상이다. 어퍼쳐 효과는 캐패시터를 기반으로 하는 샘플과 홀드 회로를 가진 ADC에서 반드시 생기는 현상이다. 왜냐하면 캐패시터는 아무런 시간 지연 없이 전압을 바꿀 수 없기 때문이다. 어퍼쳐 효과는 clock 지터에 의해서 생긴다.

$$x(t) = A\sin(2\pi f_0 t) \tag{3-1}$$

위 수식과 같은 신호를 디지털화 할 때 지터로 인한 실제 샘플링 시간 불확실성은  $\Delta t$ 로 표시된다.

$$E_{ap} \le |x'(t)\Delta t| \le 2A\pi f_0 \Delta t \tag{3-2}$$

샘플링 시간 불확실성은 위 수식으로 예상할 수 있다.

$$\Delta t < \frac{1}{2^q \pi f_0} \tag{3-3}$$

또한 지터 요구사항을 위와 같이 계산할 수 있다. q는 ADC의 비트수이다. 12비트 4MHz 샘플링의 경우  $\Delta t$ 는 19.43ps 보다 작아야 한다. 이것이 의미하는 바는 샘플링을 위해 ADC로 입력하는 클릭의 지터가 해당 값보다작아야 한다는 의미이다. 즉, 이 값보다 크게 돼서 오류가 발생한다면 원하는 시점의 샘플 값이 아닌 그 이전이나 이후의 시점의 샘플 값을 획득하게 된다.

● 지터(Jitter): 지터는 예상하고 있는 주기적인 신호의 원래의 주기 신호에 대해 발생한 원치 않은 편차이다. 원래의 주기 신호는 주로 참조 클럭에 대한 비교 값이다. 즉, 지터가 없다면 일정한 시간에 샘플링을 하게 되어 이론상으로는 1MHz 신호에 대해 4MHz 신호를 샘플링 하면 정확히 90도 간격으로 신호가 차이가 나게 된다. 지터가 있는 상태에서는 slew rate와 clock 오차의 절대 값에 따라 오차의 크기가 비례적으로 더 커진다.

$$SNR_{HF} = -10\log[2\pi * f_{INPUT} * t_{JRMS})^2 + 10^{\frac{SNR_{LF}}{10}}$$

(3-4)

위의 식은 낮은 주파수에서 SNR을 기준으로 높은 주파수의 SNR을 계산할 수 있게 해준다.

- 슬루율(Slew rate): 신호 변화의 최대 속도이다. 즉, 신호가 빨리 바뀌지 못하기 때문에 ADC에서도 왜곡이 발생한다.

- 노이즈(Noise): 서멀 센서(thermal sensor) 노이즈, 아날로그 회로 노이즈 등 등이 있다.

- 양자화(Quantization): 변환된 값을 표현하는 유한한 정확도의 워드수로 인해 발생한다.

ADC 드라이버에서 두 피드백 네트워크를 사용했고 그런 이유로 피드백 팩터도 두 개이다. 각각의 피드백 팩터와 이득은 다음의 수식으로 표현된다.

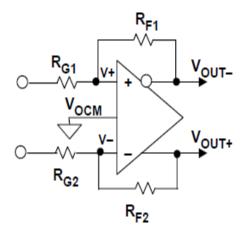

그림 3-13 ADC 입력 드라이버 블록도

$$\beta_{1} = \frac{R_{G1}}{R_{G1} + R_{F1}}$$

$$\beta_{2} = \frac{R_{G2}}{R_{G2} + R_{F2}}$$

$$Gain = \frac{2(1 - \beta_{1})}{\beta_{1} + \beta_{2}}$$

(3-5)

실제로 사용한 저항 값은 상하 같은 값이므로 다음과 같이 수식 (3-5)는 간략화될 수 있다.

$$\beta_{1} = \frac{R_{G1}}{R_{G1} + R_{F1}} = \beta_{2}$$

$$Gain = -1 + \frac{1}{\beta_{1}}$$

(3-6)

#### 제 5 절 DAC 출력 버퍼

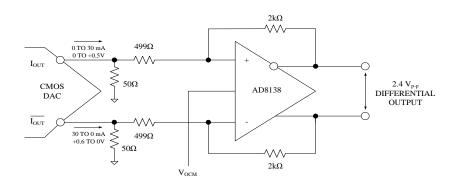

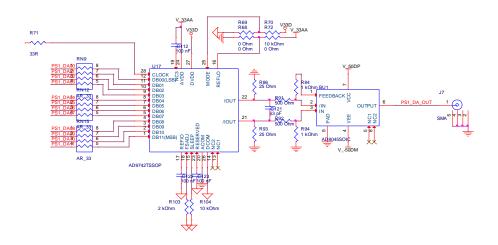

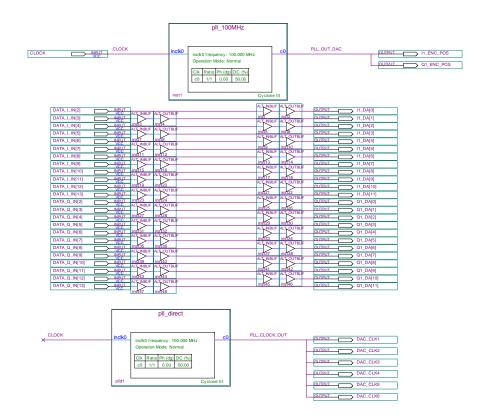

그림 3-14 사인 코사인 생성을 위한 차동 DAC 출력 버퍼

100MHz의 입력 클럭에서 1MHz의 사인과 코사인 파 생성을 위해서 사용되는 DAC 출력 버퍼이다. 출력은 차동 모드이므로 FPGA에서 사인과 코사인 파를 생성하면 0도,90도,180도,270도의 신호가 생성된다.

그림 3-15 차동 DAC 출력 버퍼 블록도

이득의 계산은 ADC 드라이버와 동일하다. FPGA에서 전류를 생성하므로 전압은

처음 만나는 50Ohm 저항을 통해서 결정된다. 다음으로 기본적으로 이 회로는 신호를 4배 증폭한다. 입력 신호 크기에 따라서 증폭 팩터를 결정하는 저항의 값은 수정해야 한다.

그림 3-16 제어 신호 생성을 위한 싱글 엔드 DAC 출력 버퍼

가변 위상 천이기와 가변 감쇄기의 전압을 제어하기 위한 DAC 출력 버퍼이다. 가변 위상 천이기와 가변 감쇄기로 전달되는 전압은 DC 이며 싱글엔드 형태로 입력을 받는다. 그러므로 DAC 출력 버퍼도 싱글엔드로 구성한다.

# 제 4 장 다중 포트 증폭기의 포트 간 격리 향상을 위한 보정 알고리즘

# 제 1 절 보정 알고리즘 개요

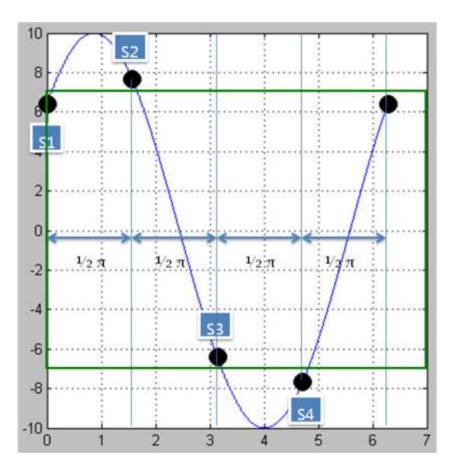

그림 4-1 이상적인 경우의 샘플링 데이터 시뮬레이션

입력 신호 보다 4배 빠른 주파수로 신호를 샘플링 하면 신호는  $1/2 \pi$  간격으로 입력된다. 그러므로 두 점이 직교하게 된다.

$$I_{\theta} = \tan^{-1}(S_{I,n+1}, S_{I,n})$$

$$Q_{\theta} = \tan^{-1}(S_{Q,n+1}, S_{Q,n})$$

(4-1)

샘플 별로 직교 하므로 atan2 함수를 한 샘플과 바로 다음 샘플에 대해서 취한다. 해당 신호의 진폭에 상관 없이 위상을 계산할 수 있다. 두 샘플이 직교하므로 진폭은 아래 수식처럼 제곱근을 통해 얻을 수 있다

$$I_{amp} = \sqrt{S_{I,n+1}^2 + S_{I,n}^2}$$

$$Q_{amp} = \sqrt{S_{Q,n+1}^2 + S_{Q,n}^2}$$

(4-2)

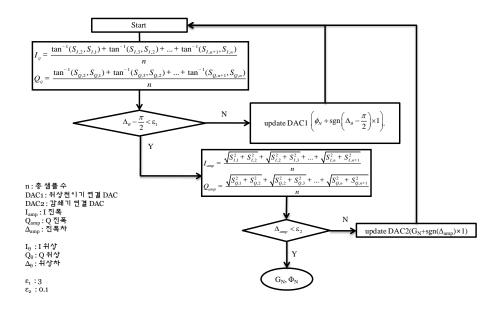

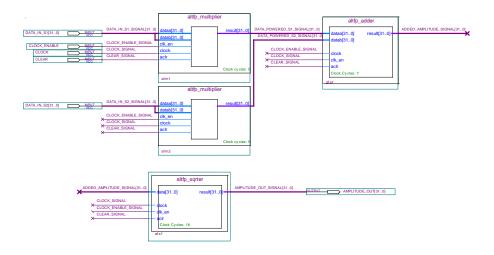

그림 4-2 한 라운드의 알고리즘

먼저, 한 라운드의 알고리즘 동작을 살펴본다. 위상은  $\mathcal{E}_1$  보다 작아지면 락이되었다고 가정한다. 진폭은  $\mathcal{E}_2$  보다 작아지면 락이 되었다고 가정한다. 위상 오차가 적을 때만 진폭을 수정한다. 위상을 수정하는 과정에서 진폭이 수정되면 오차가 커진다. 현재 이 알고리즘은 완벽한 파이프라인 방식으로 수행될 수 없다. 완벽한 파이프라인 방식으로 수행되기 위해서는 위상을 바꿀 때 감쇄 값이 전혀 바뀌지 않아야 한다. 역으로, 감쇄 값이 바뀔 때 위상이 전혀 바뀌지 않아야 한다. 하지만 실제로는 위상과 진폭이 상관성을 가지고 있다.

오차를 줄이기 위해서 샘플의 평균 값을 취한다. 샘플의 개수는  $2^{20}$  개(=1048576개) 이다. 즉, 한 라운드의 알고리즘이 동작할 때 총 1048576번 위상 값을 계산한다. 그 값의 평균 값을 특정 채널의 위상으로 정한다. 알고리즘은 적응적으로 동작하며 오차가 클 때 더 큰 값으로 찾아야 하는 값으로 수렴해 간다.

# 제 2 절 ADC 데이터의 부동 소수점 숫자 변환

ADC에서 들어오는 숫자는 2진수 비트열로 되어 있다.

표 4-1 AD6646의 입력 범위

| AIN 레벨(V) | AIN 레벨(V)   | 출력 상태 | 출력 코드             |

|-----------|-------------|-------|-------------------|

| VREF+0.55 | VREF - 0.55 | 양의 FS | 01 1111 1111 1111 |

| VREF      | VREF        | 중간값   | 00 0/11 1         |

| VREF-0.55 | VREF + 0.55 | 음의 FS | 10 0000 0000 0000 |

사용한 ADC는 Analog Device社의 AD6646이다. 이 값의 입력 범위는 위와 같다. 즉, 2의 보수 표현이다. 이를 부동 소수점 형으로 구현하는 경우 변환이 필요하다. 실제로 데이터는  $-2^{13} \sim 2^{13} - 1$ 의 수가 정수 타입의 2비트 바이너리로 입력이된다. 이를 정규화 하면 -1~1의 소수점을 가진 수로 처리할 수 있게 된다. 정규화하는 방법은 최대값으로 나눠주거나 최대값의 역수를 곱해주는 것이다. 한 번의 연산이라도 줄이는 것이 좋으므로 최대값의 역수를 곱해준다. 여기에서 2의 14비트를 예로 들면 8192로 나눠주거나 1/8192를 곱해주면 된다.

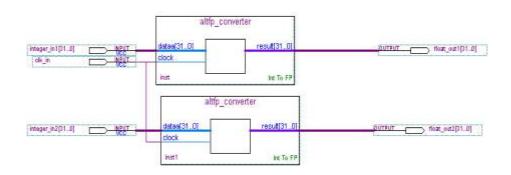

그림 4-3 32비트 정수의 binary32 형태 변환 회로 블록도

입력은 integer 타입이며 출력은 IEEE 754 single precision(binary32) 숫자로 나오게 된다. 입력으로 들어가는 integer 타입은 signed 타입이므로 시뮬레이션을 할 때도 signed 타입으로 입력한다. 비트 열은 순서대로 부호, 지수, 가수의 순서로 되어 있으며 비트열을 다 합쳐서 연결하면 부동 소수점 숫자가 된다.

십진 형태 수를 binary32로 변환하는 방법을 살펴보면 다음과 같다. 예를 들어, 28.375를 변경한다고 하면, 먼저 정수 부분을 이진수로 변경하고 정규화한다. 정규화된 숫자는 다음과 같다. 예를 들어, 219.078을 정규화하면 2.19078x10<sup>2</sup>이고, -0.00032175를 정규화하면 -3.2175x10<sup>4</sup>이 된다. 다음으로 소수 부분을 변경한다. 이때, 0.375를 바꾸면 되므로, 소수에 2를 곱해 가면서 정수가 생기면 이를 적고 남은 소수를 다음 단계로 계속 넘겨준다. 즉, 0.375를 변환하려면 다음과 같이 한다.

0.375x 2 = 0.75 = 0 + 0.75 이므로 0(정수 부분)

0.75(이전 값에서 넘어옴)x 2 = 1.5 이므로 1(정수 부분)

0.5(이전 값에서 정수부분 1을 빼고 남은 부분)x2 = 1 이므로 1(정수 부분)

소수가 없으므로 변환은 종료된다.

28을 이진수로 변경하면 11100이 되고 이를 0.375와 합치게 되면 11100.011이 된다.

이를 IEEE 754 binary32 포맷으로 변경하려면 아래 수식처럼 표현한다.

$$1.x_1x_2x_3...\times 2^y$$

(4-3)

$$1110.0011 \times 2^{1}$$

(4-4)

$$110.0011 \times 2^2$$

(4-5)

$$11.100011 \times 2^3 \tag{4-6}$$

$$1.1100011 \times 2^4$$

(4-7)

실제 시뮬레이션 결과가 같은지 확인하기 위해서 순서대로 binary32의 160, -250을 변환하면 각각 다음의 값을 가진다.

- $0 \qquad 10000110 \quad 01000000000000000000000$

- 31 30 23 22 0

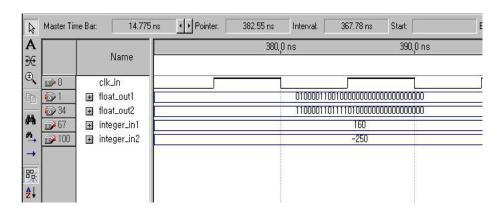

그림 4-4 32비트 정수의 binary32 형태 변환 시뮬레이션

실제로는 입력이 14비트의 2의 보수 표현이므로 이를 32비트 정수 대신 사용자정의 정수 타입으로 구현하면 다음과 같은 결과를 얻을 수 있다. 주의할 점은 최대 값과 최소값을 표현할 때, 2의 보수 타입에서 최대 값은 2<sup>N</sup> - 1의 값을 가진다는 점이다. 여기에서 N은 ADC의 비트수 이다. 최대값인 8191은 01111111111111의 값을, 최소값인 -8192는 1000000000000000를 가짐을 확인할 수 있다.

| <b>€</b>                 | Msgs              |                                         |

|--------------------------|-------------------|-----------------------------------------|

| 🥠 /test_trigometric_a/   | 0                 |                                         |

| /test_trigometric_a/     | 1                 |                                         |

| 🥠 /test_trigometric_a/   | 0                 |                                         |

| + /test_trigometric_a/   | 011111111111111   | 011111111111111                         |

| + / /test_trigometric_a/ | 00111001000000000 | 001110010000000000000000000000000000000 |

| + / /test_trigometric_a/ | 0011111101111111  | 00111111011111111111110000000000        |

| + /test_trigometric_a/   |                   | 1.0100010111111111111110000000000       |

그림 4-5 32비트 정수 최대값의 binary32 형태 변환 시뮬레이션

| <b>\$</b> 1•                    | Msgs               |                                         |

|---------------------------------|--------------------|-----------------------------------------|

| <pre>/test_trigometric_a/</pre> | 0                  |                                         |

| 🧄 /test_trigometric_a/          | 1                  |                                         |

| 🧄 /test_trigometric_a/          | 0                  |                                         |

|                                 | 100000000000000    | 1000000000000                           |

| #- /test_trigometric_a/         | 00111001000000000  | 00111001000000000000000000000000000     |

| +-> /test_trigometric_a/        | 101111111100000000 | 101111111000000000000000000000000000000 |

| + / /test_trigometric_a/        | 11000110000000000  | 110001100000000000000000000000000000    |

그림 4-6 32비트 정수 최소값의 binary32 형태 변환 시뮬레이션

알고리즘이 코드로 작성되어 문제가 없더라도 FPGA에 사용할 수 있는 자원보다 더 많은 양의 자원을 소모하도록 합성될 수 있다. 그러므로 각 블록을 구현한 후에 적은 자원을 사용하도록 최적화를 수행한다. 다음의 구현은 Altera 社의 부동 소수점형 숫자를 이용하는 메가 함수를 구현할 때 예상되는 자원 사용량이다.

표 4-2 메가 함수 구현시 에상되는 자원 사용량

| 하위 블록         | 자원                                                     |

|---------------|--------------------------------------------------------|

| ALTFP_SQRT    | 370 LUT + 761 REG # 16 cycles                          |

| ALTFP_ATAN    | 7093 LUT + + 9 M9K + 1388 REG # 36 cycles              |

| ALTFP_MULT    | 7 dsp_9bit + 111 LUT + 209 REG # 5 cycles              |

| ALTFP_ADD_SUB | 142 LUT + 347 REG # 7 cycles                           |

| ALTFP_COMPARE | 51 LUT + 1 REG # 1 cycles                              |

| ALTFP_DIVIDER | 16 dsp_9bit + 194 LUT + 1 M9K + 74 mux21 + 339 REG # 6 |

|               | cycles                                                 |

| ALTFP_INV     | 22 dsp_9bit + 467 LUT + 1217 REG                       |

# 제 3 절 진폭 계산의 부동 소수점 숫자 방식 구현

아래 그림은 샘플 2개의 값에 대해서만 진폭을 찾는다.

그림 4-7 진폭 계산의 부동 소수점 숫자 방식 구현 블록도

이 블록은 아래와 같은 자원을 소모할 것으로 예상된다. 그러므로 실제로 구현할 때는 4배 큰 자원을 소모한다.

표 4-3 진폭 계산의 부동 소수점 숫자 방식 구현 자원 소모

| 항목                                 | 값    |

|------------------------------------|------|

| Total logic elements               | 2131 |

| Total combinational functions      | 1735 |

| Dedicated logic registers          | 1134 |

| Total registers                    | 1134 |

| Total input pins                   | 67   |

| Total output pins                  | 32   |

| Total memory bits                  | 179  |

| Embedded Multiplier 9-bit elements | 14   |

#### 제 4 절 ATAN2의 부동 소수점 숫자 방식 구현

기본적으로 ATAN은 1과 4사분면에서 계산된다. 특정 IQ 신호가 1~4 모든 사분면에서 계산되도록 하기 위해서 ALTFP\_ATAN 메가 함수의 기능을 조금 수정하여 ATAN2로 구현해야 한다.ATAN2는 다음과 같이 정의된다.

$$\arctan\left(\frac{y}{x}\right), \quad x > 0$$

$$\arctan\left(\frac{y}{x}\right) + \pi, \quad y \ge 0, x < 0$$

$$\arctan\left(\frac{y}{x}\right) - \pi, \quad y < 0, x < 0$$

$$+\frac{\pi}{2}, \quad y > 0, x = 0$$

$$-\frac{\pi}{2}, \quad y < 0, x = 0$$

$$undefined, \quad y = 0, x = 0$$

$$(4-8)$$

이를 이용하여 위상을 구하기 위한 수식은 다음과 같다. 다만, x와 y가 0인 경우는 0을 출력하도록 한다.

$$\theta = \left\{\arctan\left(S_{Q,n+1}, S_{Q,n}\right) \equiv 2\pi\right\} - \left\{\arctan\left(S_{I,n+1}, S_{I,n}\right) \equiv 2\pi\right\} \tag{4-9}$$

식을 정리하여 동일한 값이 더해지거나 빼지게 하려면 총 4개의 피연산자가 필요하다. 수식에서 피연산자가 없는 경우는 상수 () 값을 더하는 것으로 한다. 또한 부동 소수점에서 부호를 표현할 수 있으므로 상수  $+\pi$ ,  $-\pi$ ,  $+\frac{\pi}{2}$ ,  $-\frac{\pi}{2}$  역시 정의를 한다. 연산은 MUX를 구현하여 수행하면 된다. (4-8)의 수식은 총 4개의 사분면에 대한 식을 나타내고 있다. 실제로는 각 항이 0일 때의 조건까지 추가해야 한다. 즉, (x가 0보다 크다.), (0보다 작다.), (0과 같다.)의 세 조건과 그에 상응하는 y의 조건까지 합치면 MUX에서 선택할 수 있는 수는 9가지이며 4비트의 선택 비트를 만들어야 한다. 어떤 연산을 선택할 지 표현은 다음과 같다.

$$Op_{MUX} = (X = 0)(X > 0)(Y = 0)(Y > 0)$$

(4-10)

선택된 조건에 따라서 수식 (4-8) 중의 한 가지 연산이 선택되어 ATAN2가계산된다.

그림 4-8 ATAN2의 부동 소수점 숫자 방식 구현의 블록도

다음은 부동 소수점 숫자 방식 구현의 ATAN2 함수가 사용하는 자원이다.

# 표 4-4 ATAN2의 부동 소수점 숫자 방식 자원 소모

| 항목                                 | 값    |

|------------------------------------|------|

| Total logic elements               | 8280 |

| Total combinational functions      | 7758 |

| Dedicated logic registers          | 1573 |

| Total registers                    | 1573 |

| Total input pins                   | 67   |

| Total output pins                  | 32   |

| Total memory bits                  | 6120 |

| Embedded Multiplier 9-bit elements | 52   |

#### 제 5 절 위상 계산의 부동 소수점 숫자 방식 구현

위상 계산에는 I 채널과 Q 채널 각각 하나씩 총 2개의 ATAN2 블록이 들어간다.

그림 4-9 위상 계산의 부동 소수점 숫자 방식 구현 블록도

ATAN2의 주변 블록은 다음과 같은 일을 수행한다. 먼저 라디안 값을 각도 값으로 변경한다. 다음으로 360도를 넘거나 음수 각도가 결과로 생성 되었을 때, 360을 더하거나 빼주는 역할을 수행한다.

표 4-5 위상 계산의 부동 소수점 숫자 방식 구현의 자원 소모

| 항목                                 | 값     |

|------------------------------------|-------|

| Total logic elements               | 18308 |

| Total combinational functions      | 17201 |

| Dedicated logic registers          | 3927  |

| Total registers                    | 195   |

| Total input pins                   | 131   |

| Total output pins                  | 64    |

| Total memory bits                  | 12474 |

| Embedded Multiplier 9-bit elements | 118   |

위상 계산을 위해서는 2개의 ATAN2 블록이 이용된다. 표 4-4의 ATAN2 구현의 소모 자원을 확인하면 표 4-5에 나타난 위상 계산 모듈에서 ATAN2의 구현이 가장 큰 자원 소모를 함을 알 수 있다.

#### 제 6 절 ADC 데이터의 고정 소수점 숫자 변환

고정 소수점형 수의 경우 소수점을 기준으로 정수 부분인 경우 양의 2의 승수를 각 비트 값에 곱하고, 소수 부분인 경우 음의 2의 승수를 각 비트 값에 곱하여 더하면 된다. 예를 들어, 3.25를 2의 고정 소수점 수로 변환하면 11.01이 된다. 14비트 2의 보수 표현인 ADC의 데이터의 경우 -1~1로 정규화 하기 위해서는 오른쪽으로 13번 쉬프트 연산을 수행하면 된다. 하지만, 문제는 정수값을 오른쪽으로 13번 쉬프트 할 경우 최소한 13비트가 오른쪽에 있어야 한다는 점이다. 실제로 입력되는 데이터 8191의 경우 1이 0.11111111111111 되어야 하므로 손실이 없는 상태로 정규화를 하려면 최소한 26비트 이상의 숫자가 필요하다.

VHDL 코드에서 sfixed(X DOWNTO Y)는 X 만큼의 정수 비트와 Y 만큼의 소수점 아래 비트를 가지고 있는 수가 된다. ADC의 디지털 값이 14비트이므로 X는 13의 값을 가진다. Y는 정규화를 하기 위한 값을 가져야 하므로 마찬가지로 13의 값을 가지게 된다. 정규화를 마친 후에 알고리즘을 처리할 때는 알고리즘에서 필요로하는 정밀도에 따라서 X와 Y의 값을 수정해야 한다.

다음의 표에서 보이듯이 특정 연산을 수행한 뒤에는 실제 나타내지고 있는 숫자의 정밀도와 상관없이 연산 벡터의 크기가 커지기 때문에 연산 중간에 정밀도를 조정하지 않으면 많은 자원을 소모하게 된다.

표 4-6 고정 소수점 연산 후 변화된 벡터 크기

| operation              | Result range                                       |

|------------------------|----------------------------------------------------|

| A+B                    | Max(A'left, B'left)+1 downto Min(A'right, b'right) |

| A-B                    | Max(A'left, B'left)+1 downto Min(A'right, b'right) |

| A*B                    | A'left+B'left+1 downto A'right+B'right             |

| A rem B                | Min(A'left, B'left) downto Min(A'right, B'right)   |

| Signed /               | A'left-B'right+1 downto A'right - B'left           |

| Signed A mod B         | Min(A'left, B'left) downto Min(A'right, B'right)   |

| Signed Reciprocal(A)   | -A'right downto -A'left-1                          |

| Abs(A)                 | A'left+1 downto A'right                            |

| -A                     | A'left+1 downto A'right                            |

| Unsigned /             | A'left-B'right downto A'right - B'left-1           |

| Unsigned A mod B       | B'left downto Min(A'right, B'right)                |

| Unsigned Reciprocal(A) | -A'right+1 downto -A'left                          |

위의 표에서 각 항은 A: A'left, B: A'right, C: B'left, D: B'right로 놓아 표기한다. A와 B는 각각 첫번째 연산자 벡터의 X DOWNTO Y에서 X값, Y값을 나타낸다. C와 D는 각각 두 번째 연산자 벡터에서 X값, Y값을 나타낸다. 즉, 다시 말하면 A와 C는 MSB를 나타내고 B와 D는 LSB를 나타낸다.

# 제 7 절 진폭 계산의 고정 소수점 숫자 방식의 구현

메가 함수로 구현했던 내용을 동일하게 VHDL-2008 Support Library의 고정소수점 숫자 형태로 다시 구현하여 자원의 사용량을 비교한다. VHDL-2008 Support Library의 사용은 고정 소수점 연산을 수행하는 것으로 연산 후 벡터의 크기를 변경시키기 때문에 반드시 벡터의 크기를 재조정할 필요가 있다[24]. 진폭 계산의 중간 단계계산에 고정 소수점 형을 이용하였기 때문에 원하는 정밀도에 따라서 블록의 자원 사용량을 조정할 수 있다. 다음은 두 가지 형태(정수.소수 표기법)의 정밀도를 이용하여 자원 사용량을 비교하였다.

표 4-7 진폭 계산의 사용 자원(3.28 비트 고정형 숫자인 경우)

| 항목                                 | 값    |

|------------------------------------|------|

| Total logic elements               | 2024 |

| Total combinational functions      | 1724 |

| Dedicated logic registers          | 613  |

| Total registers                    | 613  |

| Total input pins                   | 67   |

| Total output pins                  | 32   |

| Total memory bits                  | 121  |

| Embedded Multiplier 9-bit elements | 16   |

#### 표 4-8 진폭 계산의 사용 자원(3.14 비트 고정형 숫자인 경우)

| 항목                                 | 값    |

|------------------------------------|------|

| Total logic elements               | 1428 |

| Total combinational functions      | 1156 |

| Dedicated logic registers          | 585  |

| Total registers                    | 585  |

| Total input pins                   | 39   |

| Total output pins                  | 32   |

| Total memory bits                  | 121  |

| Embedded Multiplier 9-bit elements | 4    |

결과에서 보이듯이 정밀도를 낮추면 자원 사용량이 비례하여 감소한다. 다음은 고정 소수점 숫자 방식 진폭 계산 알고리즘을 적용할 때 결과 벡터의 크기 변화를 보인다.

ADC의 값에서 진폭을 얻기 위해서 가장 먼저 절대값을 취한다. 입력은 다음과 같은 비트 크기를 가진다.

A: 13, B: 0, C: 13: 0 D: 0

이 연산으로 sfixed(14 DOWNTO 0) 15 비트 벡터가 된다.

다음으로 이 절대값들을 각각 14비트(1 DOWNTO -12)의 알파와 베타 상수 값과곱한다. 샘플 벡터의 비트 크기는 다음과 같다.

A: 14, B: 0, C: 1 D: -12

이 연산으로 sfixed(16 DOWNTO -12)의 29 비트 벡터가 된다. 다음은 이 벡터들끼리의 합이다.

A: 16, B: -12, C: 16, D: -12

이 연산으로 sfixed(17 DOWNTO -12)의 30 비트 벡터가 된다.

다음은 최종 결과를 위해 값을 8191로 나눠주는 정규화를 하게 된다.

A: 17, B: -12, C: 13, D: 0

이 연산으로 sfixed(18 DOWNTO -25)의 44 비트 벡터가 된다. 하지만, 실제로는 최종 결과 값은 2를 넘지 않는다. 즉, 정수 부분의 값이 대부분 불필요한 0이나 1의 값을 가지게 된다는 뜻이다. 비트 부분을 제외하고 2비트를 더 추가해서 3 비트라고 가정하고 sfixed(3 DOWNTO -25)의 값을 다음 단으로 넘겨주더라도 정밀도의 손실이 없다.

여기에서 문제는 나눗셈기를 이용하여 구현하게 되면 자원 소모가 많게 된다. 그러므로 나눗셈기 대신에 쉬프트 연산으로 나눗셈을 구현한다. 여기에서 나눠져야하는 수는 2<sup>26</sup>이다. 즉, 26번 오른쪽 쉬프트 연산을 해야 한다. 하지만 부호 비트는 쉬프트 되지 않으므로 25번 오른쪽으로 쉬프트 하면 된다. 그렇다면 이전 30비트의 숫자에서 유효(significant) 숫자는 4 비트 밖에 되지 않는다. 그러므로 유효 비트의 숫자를 늘리기 위해서 원하는 정밀도만큼 연산 전에 해당 벡터의 크기를 오른쪽 방향으로 키워야 한다. 14비트의 정밀도를 얻기 위해서는 원래 벡터보다 14비트만큼 오른쪽 방향으로 더 커야 한다. 그러므로 최종 벡터는 sfixed(17 DOWNTO -26)이 된다.

# 제 8 절 Alpha Max Beta Min 크기 예상 고정 소수점 숫자 방식 구현[21]

직접적인 제곱근의 구현은 많은 자원을 소모한다. 그러므로 최소한의 오차로 근사한 값을 도출할 수 있는 알고리즘이 요구된다. 위상과 다르게 진폭의 경우 복소수에 특별한 연산을 수행하게 되면 입력 도메인이 감소하게 되고 이 감소된 도메인에 대한 값을 근사화 하면 연산이 최소화 된다. 즉, 사분면 중 1 사분면일부만 이용하여 계산할 수 있다.

표 4-9 Alpha Beta 파라미터 별 오차 범위 테스트 결과

| Name                  | Alpha          | Beta           | Avg Err<br>(linear) | RMS (dB) |

|-----------------------|----------------|----------------|---------------------|----------|

| Min RMS<br>Err        | 0.947543636291 | 0.392485425092 | 0.000547            | -32.6    |

| Min Peak Err          | 0.960433870103 | 0.397824734759 | -0.013049           | -31.4    |

| Min RMS<br>with Avg=0 | 0.948059448969 | 0.392699081699 | 0.000003            | -32.6    |

| 1-Min RMS Err         | 1.000000000000 | 0.323260990000 | -0.020865           | -28.7    |

| 1-Min Peak Err        | 1.000000000000 | 0.335982538000 | -0.025609           | -28.3    |

| 1-1/2                 | 1.000000000000 | 0.500000000000 | -0.086775           | -20.7    |

| 1-1/4                 | 1.000000000000 | 0.250000000000 | 0.006456            | -27.6    |

| Frerking              | 1.000000000000 | 0.400000000000 | -0.049482           | -25.1    |

| 1-11/32               | 1.000000000000 | 0.343750000000 | -0.028505           | -28.0    |

| 1-3/8                 | 1.000000000000 | 0.375000000000 | -0.040159           | -26.4    |

| 15/16-15/32           | 0.937500000000 | 0.468750000000 | -0.018851           | -29.2    |

| 15/16-1/2             | 0.937500000000 | 0.500000000000 | -0.030505           | -26.9    |

| 31/32-11/32           | 0.968750000000 | 0.343750000000 | -0.000371           | -31.6    |

| 31/32-3/8             | 0.968750000000 | 0.375000000000 | -0.012024           | -31.4    |

| 61/64-3/8             | 0.953125000000 | 0.375000000000 | 0.002043            | -32.5    |

| 61/64-13/32           | 0.953125000000 | 0.406250000000 | -0.009611           | -31.8    |

과정을 자세히 살펴보면, I와 Q의 샘플 값에 대해 절대값을 취하면 0~90도 사이의 값으로 제한하게 된다. 다음으로 최대와 최소 값을 취하게 되면 0~45도 사이의 값으로 제한된다. 이렇게 제한된 도메인에 대해서 특정 상수 값을 Alpha와 Beta의 값으로 선택하고 큰 샘플 값에 Alpha 작은 샘플 값에 Beta를 곱한다.

진폭의 경우 정수 부분의 최대값은 1이다. 그러므로 2의 보수 표현이라고 하더라도 2비트만 있으면 된다. 소수 부분의 해상도(resolution)가 높을수록 진폭 오차가 감소된다. 여기에서 해상도의 의미는 한 고정 소수점 표기 방식에서 한 숫자가 있을 때, 이 숫자에서 가장 가까운 크거나 작은 수까지의 간격을 의미한다. 다음은 고정 소수점 연산을 할 때 결과 벡터의 크기를 나타낸다. 곱셈기를 사용하지 않고, 매우 작은 LUT를 사용함을 알 수 있다.

표 4-10 Alpha Max Beta Min 알고리즘 구현의 자원 사용

| 항목                                 | 값   |

|------------------------------------|-----|

| Total logic elements               | 630 |

| Total combinational functions      | 630 |

| Dedicated logic registers          | 38  |

| Total registers                    | 38  |

| Total input pins                   | 59  |

| Total output pins                  | 84  |

| Total memory bits                  | 0   |

| Embedded Multiplier 9-bit elements | 0   |

그림 4-10 진폭 오차 시뮬레이션

진폭 오차의 값을 정확히 찾는 지 여부를 판단하기 위한 시뮬레이션에서는 실제 ADC에서 얻은 데이터가 필요하다. 진폭과 위상 오차 시뮬레이션에서 ADS4226EVM과 TSW1200EVM에서 얻은 데이터를 이용했다. 이 평가 보드들은 14비트 160MSPS까지 샘플링을 지원하지만, 4MSPS로 동작시켰고, 2의 보수 표현의데이터를 두 비트씩 쉬프트하여 실제 사용하는 ADC의 샘플링 비트 수와 일치시켰다.

그림 4-11 시뮬레이션 데이터 생성을 위한 Texas Instrument社의 평가보드

위의 그림은 시뮬레이션 데이터 생성을 위한 평가 보드를 보인다. 아래는 100MHz로 샘플링한 IQ 데이터를 보인다.

그림 4-12 평가 보드에서 샘플링한 데이터

# 제 9 절 자가 정규화 ATAN2 고정 소수점 숫자 방식 구현[22]

x=real(z), y=imaginary(z)라고 하고, 복소수 z가 1 사분면에 있을 때, 다음과 같이 비율과 위상을 근사하여 계산할 수 있다.

$$r_1 = \frac{x - y}{x + y} \tag{4-11}$$

$$\theta_1 = \frac{\pi}{4} - \frac{\pi}{4} r \tag{4-12}$$

복소수 z가 2 사분면에 있다면, 다음과 같다.

$$r_2 = \frac{x+y}{y-x} \tag{4-13}$$

$$\theta_2 = \frac{3}{4}\pi - \frac{3}{4}\pi * r \tag{4-14}$$

복소수 z가 3 사분면에 있다면, 다음과 같다.

$$r_3 = \frac{x+y}{y-x} \tag{4-15}$$

$$\theta_3 = -\frac{3}{4}\pi + \frac{3}{4}\pi r \tag{4-16}$$

복소수 z가 4 사분면에 있다면, 다음과 같다.

$$r_4 = \frac{x - y}{x + y} \tag{4-17}$$

$$\theta_4 = -\frac{\pi}{4} + \frac{\pi}{4} r \tag{4-18}$$

여기에는 최대 0.07rad 정도의 오차가 있으며 이는 4도 정도이다. 더 나은 정확도를 얻으려면 다음을 이용할 수 있다.

$$\begin{aligned} \theta_1 &= 0.1963 * r^3 - 0.9817 * r + \frac{\pi}{4} \\ \theta_2 &= 0.1963 * r^3 - 0.9817 * r + 3 * \frac{\pi}{4} \\ \theta_3 &= -0.1963 * r^3 + 0.9817 * r - 3 * \frac{\pi}{4} \\ \theta_4 &= -0.1963 * r^3 + 0.9817 * r - \frac{\pi}{4} \end{aligned}$$

$$(4-19)$$

이 경우 최대 0.01 rad정도의 오차가 있으며 이는 0.5도 정도이다.

표 4-11 자가 정규화 ATAN2 알고리즘 자원 사용

| 항목                                 | 값    |

|------------------------------------|------|

| Total logic elements               | 3431 |

| Total combinational functions      | 3431 |

| Dedicated logic registers          | 106  |

| Total registers                    | 106  |

| Total input pins                   | 31   |

| Total output pins                  | 78   |

| Total memory bits                  | 0    |

| Embedded Multiplier 9-bit elements | 24   |

이는 부동소수점 형 ATAN2 구현에 비해 1/5배 정도 자원을 소모한다.

그림 4-13 위상 오차 시뮬레이션

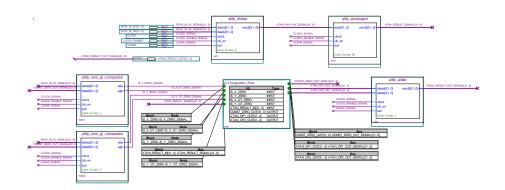

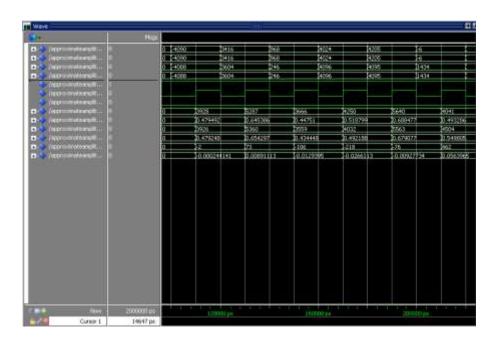

## 제 10 절 전체 IQ 보정 알고리즘의 고정 소수점 숫자 방식 구현

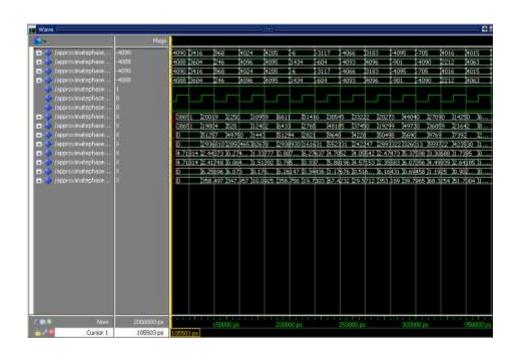

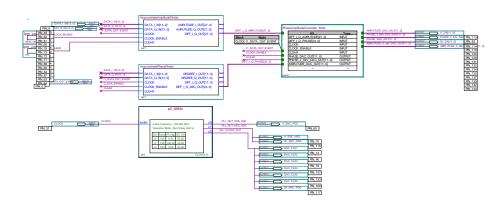

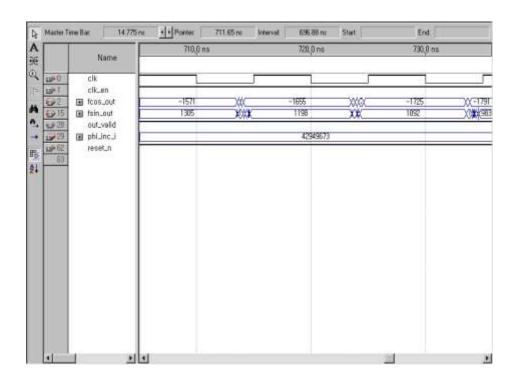

그림 4-14 전체 IQ 보정 알고리즘 구현

위 그림은 FPGA 보드에 핀 매핑까지 완료한 IQ 보정 알고리즘의 전체 구현이다. 동작 클럭은 100MHz이다. ADC에서 들어온 데이터는 공유한다. 다만, 진폭과위상에서의 정밀도가 다르기 때문에 고정 소수점 숫자로 바꿀 때 비트 수는다르다. ADC 신호는 실시간으로 입력되고 지연없이 한 클럭 안에 결과를 출력한다.현재 입력 신호의 위상과 진폭을 계산한다. 하지만, 갱신은 100MHz로 하게 되면DAC에서 위상 천이기와 감쇄기에 DC 전압이 전달되는 것이 아니라 100MHz주파수를 가진 신호가 생성되기 때문에 위상 천이기와 감쇄기의 특성에 큰 영향을미칠 수가 있다. 그러므로 DAC의 신호 생성 속도는 ADC 동작 속도와 동일하게한다. 또한 데이터의 갱신은 계속 이뤄지지만 잘못된 값을 가지지 않도록 평균값을 이용한다.

표 4-12 전체 알고리즘에서 사용한 자원

| 항목                                 | <b></b> |

|------------------------------------|---------|

| Total logic elements               | 3621    |

| Total combinational functions      | 3621    |

| Dedicated logic registers          | 132     |

| Total registers                    | 132     |

| Total input pins                   | 30      |

| Total output pins                  | 58      |

| Total memory bits                  | 0       |

| Embedded Multiplier 9-bit elements | 24      |

| Total PLLs                         | 1       |

구현한 가변 위상 천이기와 감쇄기는 서로 위상과 크기에 큰 영향을 미치지 않고 변화된다. 위상은 두 샘플을 측정할 때 진폭이 변화하지 않아야 하는 조건이 있다. 만약 1번 샘플을 가지고 있고 아직 2번 샘플을 가져 오지 않은 상태에서 감쇄기의 값이 바뀌어서 2번 샘플의 크기가 달라진다고 가정한다. 2번은 현재 위상 값에서 원래 가지고 있어야 하는 값보다 크거나 작을 것이다. 이는 즉시 위상 오차로 나타나게 된다. 즉, 이는 알고리즘이 수렴할 수 없게 되는 조건이 된다. 그러므로 진폭 오차의 수정은 위상 오차가 거의 없어진 상태에서 수행된다.

#### 제 11 절 NCO의 구현

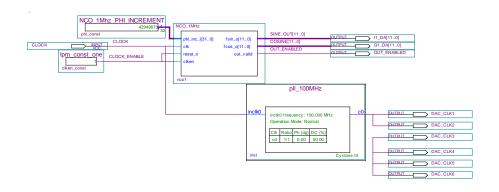

NCO 메가 함수은 코사인과 사인 파형의 디지털 값을 생성하기 위해서 이용한다. phi\_inc\_i는 해당 위상 누적 값이다. clk는 입력이며, reset\_n과 clk\_en은 high로 두어야한다. out\_valid가 high가 된 이후로 fsin\_out, fcos\_out의 값이 이용 가능한 값이 된다.

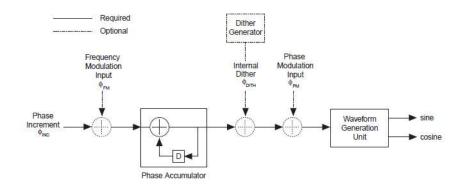

그림 4-15 NCO 블록도

그림 4-16 NCO의 동작 방식

생성 알고리즘은 CORDIC - 병렬 모드 이며, 구현 방식은 위상 누적기 방식, 정밀도가 32비트, 각 해상도이 16비트, 진폭 해상도가 12비트(DAC의 성능과 동일해야 함), 이중 출력, 위상 디더링 활성화 이다. 입력 주파수는 전역 클럭과 동일하게 하며 출력은 1MHz를 설정하여 사인과 코사인 파에 해당하는 디지털 값이 생성되도록 한다. 파형은 다음의 수식으로 표현된다.

$$s(nT) = A\sin[2\pi((f_O + f_{FM})nT + \phi_{PM} + \phi_{DITH})]$$

(4-20)

여기에서 T는 동작 클릭 주기이며,  $f_O$ 는 입력된 위상 증가 값인  $\phi_{INC}$  값을 기준으로 계산된 복조되지 않은 출력 주파수이며,  $f_{FM}$  은  $\phi_{FM}$  을 기준으로 계산된 주파수 변조 파라미터이며,  $\phi_{PM}$  은 위상 변조 입력 값 P와 P의 비트  $2 \log (P_{width})$ 를  $\phi_{PM} = 2^{\frac{P}{P_{width}}}$ 에 의해 계산한 값이다.  $\phi_{DIIH}$ 는 내부 디더링 값이며, A는 N이 크기의 정밀도일 때  $2^{N-1}$ 의 값이다.

$$f_O = \frac{\phi_{inc} f_{clk}}{2^M} Hz \tag{4-21}$$

여기에서  $2^M$  은 위상 누적기의 정밀도이다. 계산된 위상 증가 값은 42949673이며, 즉, 위의 공식에 따르면 42949672.96의 값이 반올림 된 값임을 알 수 있다. 또한 이 때문에 1MHz 대신 1.00000000009313226 MHz가 실제 출력 주파수가된다.

그림 4-17 NCO 1MHz 사인 코사인 생성 시뮬레이션

-1~1의 사인과 코사인 값 대신 12 비트 DAC를 위한 값으로 크기 변환되어 출력됨을 확인할 수 있다.

표 4-13 NCO 구현의 소모 자원

| 항목                                 | 값    |

|------------------------------------|------|

| Total logic elements               | 1060 |

| Total combinational functions      | 988  |

| Dedicated logic registers          | 1035 |

| Total registers                    | 1035 |

| Total input pins                   | 1    |

| Total output pins                  | 31   |

| Total memory bits                  | 78   |

| Embedded Multiplier 9-bit elements | 0    |

| Total PLLs                         | 1    |

## 제 12 절 입력되는 I와 Q 채널 신호의 확인

그림 4-18 ADC-DAC 직접 연결 블록도

Analog Device 社의 14비트 ADC인 AD6646와 같은 회사의 12 비트 DAC 인AD9742를 이용한다. ADC의 입력 값을 쉬프트하는 동작을 위해서 ADC 출력을 DAC의 입력으로 2비트씩 이동시켜 연결한다. ADC와 DAC의 클락 속도를 동일하게하여 동기를 맞춘다.

그림 4-19 ADC에 입력된 1MHz 복조된 사인 코사인 파형

문제는 위와 같이 ADC의 내부 스위칭 캐패시터의 샘플-홀드로 인한 스위칭 전이로 인해서 중간 지점을 기준으로 많은 노이즈가 보이고 있다. 또한 클락의 부정합으로 인해 정확한 빼기 연산이 되지 않고 역상의 신호가 같이 인가되는 것처럼 보이고 있다.

그림 4-20 평균을 취해 임펄스 신호를 줄인 복조 신호의 성상도

이러한 노이즈 문제는 샘플의 값을 바로 이용하지 않고 평균 값을 취하여 이용하면 완전히 없앨 수는 없지만 개선할 수 있다.

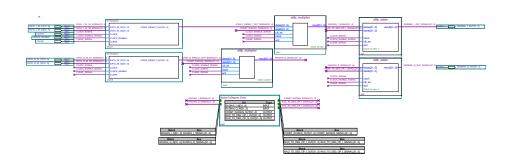

# 제 5 장 MPA 검증 모듈의 측정

## 제 1 절 전체 구성

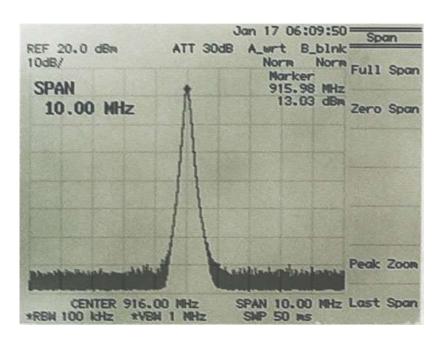

실험의 구성은 다음과 같다. 916MHz의 RF신호를 ICH1으로 인가한다. LO 입력 포트에 917MHz의 신호를 인가한다. OCH1과 OCH2는 각각 스펙트럼 분석기에 연결한다. 알고리즘이 진행됨에 따라 OCH2의 신호가 최소화 되어 격리도가 향상되는지 여부를 확인한다.

그림 5-1 IQ 보정 알고리즘 검증을 위한 실험 구성(가변형 복조기)

그림 5-2 IQ 보정 알고리즘 검증을 위한 실험 구성(고정형 복조기 + 디지털 위상 오프셋)

가변형 복조기의 경우 복조기의 위상 오차가 있을 경우 복조기의 위상 천이기와 감쇄기의 전압을 조정하여 위상 및 진폭 오차를 조정한다. 고정형 복조기는 위상 오차가 있을 경우 디지털 오프셋 값을 조정하여 위상 오차를 조정한다. 연결된 복조기가 보정이 된 상태라고 가정했을 때, RF 입력 파워가 다름에도 불구하고 유사하게 동작하는지 여부를 확인한다.

## 제 2 절 측정 결과

#### 표 5-1 가변형 복조기를 이용한 측정 결과

| 항목                   | 값                   |

|----------------------|---------------------|

| 입력 RF신호(ICH1)        | 916MHz@4.48dBm      |

| 입력 LO 신호             | 917MHz@8.53dBm      |

| 복조기 위상 천이기 전압 값      | 2.38V               |

| 복조기 감쇄기 전압 값         | 0.523V              |

| 위상 및 진폭 값 평균 값 계산을 위 | 2 <sup>20</sup> 7]] |

| 한 샘플 개수              | - /                 |

| 출력 RF 신호(OCH1)       | 916 MHz@13.03dBm    |

| 출력 격리 신호(OCH2) – Max | 916 MHz@-35.06dBm   |

| 출력 격리도 - Max         | 48.09dB             |

| 출력 격리도 - Typical     | 20dB                |

#### 표 5-2 고정형 복조기를 이용한 측정 결과

| 항목                   | 값                   |

|----------------------|---------------------|

| 입력 RF신호(ICH1)        | 916MHz@-12.44dBm    |

| 입력 LO 신호             | 917MHz@8.53dBm      |

| 복조기 위상 오프셋           | -82.5도              |

| 위상 및 진폭 값 평균 값 계산을 위 | 2 <sup>20</sup> 7]] |

| 한 샘플 개수              | <b>2</b> / II       |

| 출력 RF 신호(OCH1)       | 916MHz@-4.47dBm     |

| 출력 격리 신호(OCH2) – Max | 916MHz@-44.354dBm   |

| 출력 격리도 - Max         | 39.884dB            |

| 출력 격리도 - Typical     | 18dB                |

가변형 복조기와 고정형 복조기 어느 것을 이용하더라도 대략 18dB~20dB 정도의 격리도 향상을 가져왔다. 실험은 다른 RF 입력 전력 크기를 이용했으나 결과는 크게 다르지 않음을 보인다.

그림 5-3 OCH1에서의 출력 전력 (가변형 복조기)

그림 5-4 OCH2에서의 출력 전력 (가변형 복조기)

그림 5-5 OCH1에서의 출력 전력 (고정형 복조기)

그림 5-6 OCH2에서의 출력 전력 (고정형 복조기)

- 105 -

제어 신호를 찾은 경우 해당 DC 값에서 큰 변화 없이 락이 된 상태로 머물러 있는 것을 확인할 수 있었다. 다만, 복조기의 보정이 잘못된 경우 잘못된 전압 값에서 락이 된다.

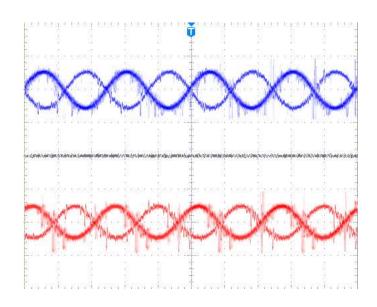

그림 5-7 알고리즘 적용 전의 MPA 출력 신호

위 그림은 알고리즘 적용 전의 MPA 출력 신호를 보인다. OCH1과 OCH2의 신호 크기에 큰 차이가 없음을 확인할 수 있다.

그림 5-8 알고리즘 적용 후의 MPA 출력 신호

위 그림은 알고리즘을 적용 후의 MPA 출력 신호를 보인다. OCH2의 신호가 OCH1에 비해서 매우 큼을 알 수 있다. 이는 격리도가 높아졌기 때문에 얻어지는 결과이다. 즉, 높은 격리도가 얻어진 결과를 보인다.

#### 제6장 결론

위성 통신 복합탑재체 설계에서 유연성을 높이기 위해서 다중 포트 전력 증폭기가 이용되며, 이 때 다중포트 전력 증폭기의 출력 포트 간 높은 격리도 유지는 본 연구의 핵심 주제이다. 본 연구에서는 7-포트 상관기(복조기) 구조를 통해 복조한 사인 파형 신호를 기저 대역에서 처리하여 높은 격리도를 획득한다.

이를 위해서 본 연구에서는 UHF 대역에서 동작하는 MPA 모듈과 7-포트 복조기를 검증 모듈로서 제작했다. 또한, Altera 한 PFGA 칩을 이용하여 FPGA 보드를 제작하여 알고리즘의 동작함을 확인하였다. 제작한 UHF 대역 MPA 모듈은 먼저 917MHz의 LO 신호를 I와 Q 채널의 신호로 분할한다. 증폭기를 통과한 각신호는 커플링되어 복조기를 통해 직접 하향 변환되어 FPGA 보드로 전달된다. 3-dB 커플러는 -3.5dB의 감쇄를 가지고 있다. 위상 천이기는 0~5V 전압에서 1.04~1.31dB의 감쇄가 일어나는 동안 96.02도의 위상이 변한다. 가변 감쇄기는 0~0.5V 전압에서 1.17~3.1dB의 감쇄가 일어나는 동안 0.6도의 위상이 변한다. 전력 증폭기는 13.7dB의 이득을 가지고 있으며, 10dB 커플러에서 9.86dB가 감소된 신호를 복조기로 전달된다. 즉, 입력된 RF 신호는 3.8dB~2.14dB의 감쇄를 가지고 복조기에 전달된다. 가변형 복조기의 경우에 복조기에서 최소 2.21dB의 손실이 있고, 다시 3-dB 커플러를 통해서 7dB의 손실이 있다. 최종적으로 RF I와 Q 신호는 13.01~11.35 dB 감소된 신호가 전달된다. 고정형의 경우, 10.8~9.14 dB의 감소된 신호가 전달된다. 보조기에 입력된 LO 신호는 전력 분배기를 통과하여 3-dB 커플러를 통해서 7dB의 손실이 있다.

FPGA 보드를 제작하는데 Altera社의 EP3C25Q240C8N Cyclone III 칩을 이용했다. FPGA는 100MHz 클럭 속도로 위상과 진폭 오차를 계산하여, I와 Q 채널 신호 경로의 위상 천이기와 감쇄기에 대해 0~5V 전압 값을 생성한다. 가장 먼저

ADC드라이버를 통해 오프셋이 조정되고 증폭된 I-Q 차동 신호는 2의 보수 형태의 정수로 디지털화 된다. 알고리즘은 정밀도를 잃지 않기 위해 정수에서 소수점이 있는 숫자로 변환한다. 부동 소수점 숫자의 구현은 정확도가 매우 높으나 많은 자원을 소모한다. 이런 문제를 해결하기 위해서 고정 소수점 숫자로 알고리즘을 구현한다. 위상 오차는 직교하는 I-Q 채널의 두 샘플에 대해 ATAN2를 통해 구할수 있다. 하지만, ATAN2의 직접적인 구현은 많은 자원을 소모한다. 그러므로 스스로 정규화를 수행하는 ATAN2 근사 공식으로 이를 구현한다. 진폭은 제곱근 공식을 대신하기 위해서 Alpha Max Beta Min 근사 방법으로 구현한다.

UHF 대역 검증용 모듈, 가변형 복조기, FPGA 보드를 연결하여 다음과 같은 실험을 진행한다. 입력 포트 ICH1에 4.48dBm@ 916MHz의 RF 신호를 인가한다. 그리고 RF Input 포트에 8.53dBm@ 917MHz의 신호를 인가한다. 출력 포트 OCH1과 OCH2는 각각 스펙트럼 분석기에 연결한다. 알고리즘이 진행됨에 따라 OCH2의 신호가 최소화 되어 격리도가 향상되어 최대 47.74dB, 일반적으로 20dB의 출력 격리도를 얻었다. 고정형 복조기를 이용한 실험에서 -12.44dBm@916MHz의 RF 신호를 인가하고, 위상 오프셋을 -82.5도로 준 후에 나머지는 가변형 복조기 실험과 동일하게 실험하여 최대 39.884 dB, 일반적으로 18 dB의 출력 포트간 격리도를 얻었다.

정리하면, 본 연구에서는 UHF 대역 검증 MPA 검증 모듈을 통해 알고리즘이 출력 포트간 높은 격리도를 얻기 위해 사용될 수 있음을 검증하였다.

#### 참 고 문 헌

- [01] M. J. Mallison, and D. Robson, 2001, "Enabling Technologies for the Eurostar Geomobile Satellite", 19th AIAA International Communications Satellite Systems Conference.

- [02] J.L. Butler, Jun, 1960, "Multiple Beam Antenna System Employing Multiple Directional Couplers in the Leadin", US Patent 3255450.

- [03] W.A. Sandrin, 1974, "The Butler Matrix Transponder", COMSAT Technical Review, vol. 4, no. 2.

- [04] D.J. Whalen, and G. Churan, 1992, "The American Mobile Satellite Corporation Space Segment", 14th AIAA International Communications Satellite Systems Conference.

- [05] A.G. Roederer, 1990, "Multi-beam Antenna Feed Device", US Patent No. 5115248, September.

- [06] D. Greenwood, J. Griffin, and A. Roederer, 1991, "Multimatrix Beam Forming for Semiactive Antennas at L-band", ESA Workshop on Advanced Beamforming Networks for Space Applications, ESTEC, Noordwijk, The Netherlands.

- [07] A. Sbardellati, T. Sassorossi, M. Marinelli, and R. Giubilei, 1994, "The Communication Payload of the Artemis European Satellite", 15th AIAA International Communications Satellite Systems Conference.

- [08] M. Lisi, 1989, "A 20/30 GHz Multiple Beam Adaptive Antenna for Satellite Trunk Communications", International Conference on Electromagnetics in Aerospace Applications, Torino, Italy.

- [09] M. Lisi, and G. Perrotta, 1989, "An Integrated 20/30 GHz Multibeam/Multiport Antenna System for Fixed Satellite Services", Proceedings of the ISAP, Tokyo, Japan.

- [10] I. Hosoda, T. Kuroda, Y. Ogawa, and M. Shimada, 15-17, May, 2007, "Ka-band High Power Multi-port Amplifier (MPA) Configured with TWTA for Winds Satellite", IEEE International Vacuum Electronics Conference, IVEC '07.

- [11] Piero Angeletti, and Marco Lisi, May 2010, "Multiport Power Amplifiers for Flexible Satellite Antennas and Payloads", Microwave Journal, vol. 53, no. 5, pp. 96.

- [12] A. Mallet, A. Anakabe, J. Sombrin, R. Rodriguez, and F. Coromina, 11-16, Jun, 2006, "Multi-Port Amplifier Operation for Ka-band Space Telecommunication Applications", Microwave Symposium Digest 2006, IEEE MTT-S International.

- [13] Zhiwen Zhu, Xinping Huang, and Caron, M, 13-19, Jun, 2010, "Ka-Band Multi-port Power Amplifier Calibration Experiment and Results", pp. 11–14, 2010 Second International Conference on Advances in Satellite and Space Communications (SPACOMM).

- [14] Mallet, A., Anakabe, A., Sombrin, J., and Rodriguez, R., Dec, 2006, "Multiport-Amplifier-Based Architecture Versus Classical Architecture for Space Telecommunication Payloads", vol. 54, no. 12, pp. 4353-4361, IEEE Transactions on Microwave Theory and Techniques.

- [15] S. Chen, Y. Hsieh, 22, Sep, 2006, "IQ Calibration Techniques for CMOS Radio Transceivers (Analog Circuits and Signal Processing), Springer.

- [16] A. D. Couchman, D. R. Jones, 24, Jun, 2010, "Multiport Amplifiers in Communications Satellites", no. US2010/0156528.

- [17] 강민수, 강원태, 장익수, 9월 1997년, "반사형 저위상 변화 감쇄기의 설계", 전자 공학회논문지, 제 34권, D 편, 제 9호.

- [18] Altera AN-39. "IEEE 1149.1 JTAG Boundary-Scan Testing in Altera Devices", Altera

- [19] Walt Kester, "Analog Digital Conversion", Newnes, Dec, 16, 2004.

- [20] D. M. Pozar, 12, Aug, 1997, "Microwave Engineering", Wiley.

- [21] M. Frerking, Jan, 1994, "Digital Signal Processing in Communication Systems", Springer.

- [22] Jim Shima, 23, Apr, 1999, "Fixed-Point Atan2 with Self Normalization".

- [23] http://en.wikipedia.org/wiki/Sampling\_(signal\_processing)

- [24] http://www.eda.org/fphdl/

#### **Abstract**

# A study on the control of amplitude and phase of multiport amplifier

EunCheon Lim.

Department of Electrical and

Computer Engineering

Graduate School of Engineering

The University of Seoul

(Supervised by Professor,

Moon-Que Lee, Ph. D.)

In recent design of satellite payload, the multiport power amplifier (MPA) has been utilized. The MPA is capable of controlling output power level and is less vulnerable to failures. With these merits, high isolation among output ports should be achieved to apply the MPA to payload architectures. Especially, in high frequency application such as K-band MPA, the power amplifiers have individual variations in characteristics so that it is not easy to control them and achieve the ideal isolation.

In this research, we propose an I-Q calibration algorithm enabling high isolation among MPA output ports by driving the voltage on variable phase shifter and attenuator applied on the RF signal path. The algorithm has been developed to find the phase and amplitude mismatch and programmed in an Altera Cyclone III FPGA chip. As a prototype module for demonstration of the proposed algorithm, we have designed a UHF-band MPA and calibration block using 7-port demodulator. The 7-port demodulator structure allows converting radio-frequency signals into

base-band signals without intermediate frequency. The voltage controlled phase shifter changes the phase in range of 96.02 degree with the insertion loss of 1.04 dB. The voltage controlled attenuator modifies the insertion loss ranged from 1.17 to 3.1 dB with 0.6-degree phase shift. Two DAC voltages driving the phase shifter and attenuator are generated from the FPGA. The voltage variations of phase shifter and attenuator due to the DAC output buffer determine the balance of attenuation and phase between two RF signal paths.

The first algorithm manipulates floating point numbers to maintain highest precision during entire calculation. However, the cost of resource was too high to be fit in the FPGA device. Instead, we replace the floating point numbers into fixed point numbers for optimal resource utilization. The direct implementation of the arctangent and square root is simple and intuitive but the efficiency and resource utilization are degraded significantly. For more efficiency, the approximated method was successfully applied.

The final full-path test shows the performance and feasibility of the algorithm. We have tested the algorithm with different input power and type of demodulator. The first test configuration for variable type demodulator has following parameters: input RF power of 4.48 dBm at 916 MHz, input LO power of 8.53 dBm at 917 MHz, voltage of phase shifter of 2.38 V, and voltage of attenuator of 0.523 V. Using the proposed algorithm, we have obtained 47.74 dB port isolation at the best and 20 dB for typical. For fixed type demodulator the test configuration has the following parameters: input RF power of -12.44 dBm at 916 MHz, demodulator phase offset of -82.5 degree. The other parameters are the same with the first test configuration. The result shows the isolation of 40.0 dB at the optimal condition and normally 18.0 dB.

In conclusion, the algorithm demonstrates its capability to find optimal phase and amplitude according to the RF I and Q signals from the 7-port demodulator MPA prototype module in UHF band.

Keywords: Multiport Amplifier (MPA), Isolation, Satellite Payload, Butler Matrix, IQ

Calibration Algorithm, Modulator/Demodulator Circuit, Field Programmable Gate Array (FPGA), Very High Speed Intergrated Circuit Hardware Description Language (VHDL)

# 이력서

● 성 명: 임은천

● 생년월일: 1982년 07월 02일

● 주소지: 전남순천시

● 홈페이지: http://javawide.com

## 학 력

- 2010.08/30.-2012.08.22. 서울시립대학교 전자전기컴퓨터공학과 석사 졸업

- 2007.03.02.-2009.02.25. 순천대학교 정보통신공학부 멀티미디어공학과 석사 졸업

- 2001.03.02.-2007.02.23. 순천대학교 정보통신공학부 컴퓨터과학과 수석 졸업

- 1998.03.02.-2001.02.10. 순천고등학교

#### 연구실적

- 참여 연구: 4 건

- [01] "다중포트증폭기의 진폭 및 위상 제어", ETRI, 2011.06.01-2012.01.31.

- [02] "고효율 RF 인버터 설계", ETRI, 2010.07.01-2010.12.31.

- [03] "복합 탑재체 신호원 구성 분석", ETRI, 2010.05.16-2010.11.30.

- [04] "RFID의 인식거리 확장을 위한 송수신 신호 분리 특성을 갖는 쿼드리필러 타입 안테나 모듈", 서울시정개발연구원, 2010.03.01-2011.10.31.

- 강의 보조:4 회

- [01] "초고주파 공학 설계 실습", Prof. 오경섭, 2011.08.30-2011.12.28.

- [02] "캡스톤 설계", Prof. 이문규, 2011.08.30-2011.12.28.

- [03] "캡스톤 설계", Prof. 이문규, 2011.03.03-2011.06.27.

- [04] "초고주파 공학 설계 실습", Prof. 이문규, 2010.09.08-2010.12.27.

- 국제 학술대회: 2 편

- [01] "A Study on a Framework for Persistence Layer Supportable Web Services in Distributed Environments" (Accepted), <u>Eun-Cheon Lim</u>, Se-Hoon Jung, Chun-Bo Sim, International Conference on Convergence and Hybrid Information Technology (ICHIT) 2012, 1, Jun, 2012

- [02] "UHF-band RFID Reader Front-end Architecture using Ring-hybrid for Near-field Applications", Donghoon Park, <u>Eun-Cheon Lim</u>, Kai Wei, Hye-Mi Park, Sang-bo Min, Jong-Won Yu, Moon-Que Lee, 41st European Microwave Conference, Poster 03-3, 13, Oct, 2011

- 국내 학술지: 2 편

- [01] "송수신 격리특성을 개선한 RFID 안테나 모듈"(**우수논문**), 박동훈, 김귀성, 김 형은, 박혜미, 위개, <u>임은천</u>, 이문규, 전기학회논문지, 제 60권, 제 2호, p. 370-375, 2011.02.01

- [02] "객체지향 설계 유형 및 도메인 객체 인터페이스를 이용한 논문 투고 관리 시스템 설계 및 구현", 심춘보, 정세훈, 임은천, 유강수, 한국 전자통신학회 논문지, 제 5권, 제 5호, p-449-458, 2010. 10.15

- 국내 학술대회: 3 편

- [01] "근거리 무선 전력 전송을 위한 10W급 RF Power Source 설계", 박동훈, 김귀성, 임은천, 박혜미, 이문규, 대한전기학회 제 42 회 하계학술대회 논문집, p. 1648-1649. 2011.07.22

- [02] "근거리 무선 전력전송을 위한 고효율 광대역 RF Power Source 설계", 김귀성, 임은천, 이문규, 추계 마이크로파 및 전파전파 학술대회, P-5-11, 2010.10.01

- [03] "송수신 격리 특성을 개선한 RFID 안테나 모듈", 박동훈, 김귀성, 김형은, 박혜

미, 위개, **임은천**, 이문규, 대한전기학회 하계학술대회 2010.07.15

● 특허 등록:1 건

[01] "근접장 응용을 위한 RFID 신호처리 장치", 이문규, 박동훈, 유종원, 민상보, 박혜미, Kai Wei, **임은천**, South Korea, 등록 번호: 10-2011-0005419

#### 감사의 글

먼저 2년 간 마음 고생 하시면서 저를 지도하여 주신 이문규 교수님께 죄송하다는 말씀과 감사하다는 말씀을 전하고 싶습니다. 비록 교수님의 기대에 많은 부응을 해드리지 못하고 사고만 많이 일으켰지만 정말 많은 것을 배울 수 있었습니다. 또한, 이문규 교수님, 그리고 카이스트의 오경섭 박사님의 강의 보조를할 기회를 얻게 되어서 좀 더 RF 분야에 관심을 가질 수 있었습니다.

특히, ETRI 위탁 과제인 "다중 입출력 증폭기의 위상 및 진폭 제어 연구"를 주도적으로 수행할 수 있도록 해주신 것을 진심으로 감사드립니다. 이 과정에서 정말 많은 분들께 고민거리를 드렸던 것 같습니다. 이러한 기회를 주신 교수님뿐 아니라 성모 형님께도 큰 감사 드립니다. 디지털 회로 제작뿐만 아니라 인생에 대한 새로운 가능성을 열어주신 창원의 김기준 선생님께 감사드리고 이 프로젝트에 마찬가지로 많은 도움을 주신 MMCL의 이경보 선생님께도 큰 감사드립니다.

비록, 제가 다른 학교에서 학위를 하고 있음에도 불구하고, 지속적으로 저에게 큰 관심과 전폭적인 지지를 해주신 심춘보 교수님께도 감사드립니다. 제가 이전에 작성해 둔 논문을 마무리 지어주시고, 언제나 해주시는 인생에 대한 조언은 저에게 큰 힘이 됩니다. 그리고 멀리 있어서 내가 해야하는 일 일부를 해준 정세훈, 김경종, 권용욱, 양병렬에게도 고맙다는 말을 전하고 싶습니다.

성격이 맞지 않아 여러 안 좋은 일들도 있었지만, 연구실 처음 왔을 때부터 나갈 때까지 계속 많은 것을 알려주려고 노력해주신 박동훈 형님께도 미안하고 고맙다는 말씀을 전합니다. 석사 선배지만 같은 나이인 김귀성, 선배지만 더 어린 김형은, 모두 자기가 맡은 일에 최선을 다해서 성공한 모습으로 봤으면 좋겠다.

자기 일이 아니지만 같이 잠도 안자면서 회로 제작 및 측정, 각종 그림 그리기,

이론에 대한 설명 등 지속적으로 제일 많은 도움을 준 위개(Wei Kai)에게 고맙다는 말을 하고 싶다. 또한, 마찬가지로 회로 제작도 도와주고, 행정적으로 보조를 해준박혜미도 고마워.

학부 졸업 후 연구실을 떠났지만, 가끔 조언을 구하기도 했던 김민식, 신지수, 둘다 꼭 하는 일 성공하길 바랄께. 그리고, 오래 보지는 못했지만, 이것저것 도움을받았던 학부생 동현준과 박인준, 이상권도 고맙다.

마지막으로 학문적 욕심이 너무 큰 아들 뒷바라지 하시느라 아직도 일하고 계신 아버지와 어머니께 지켜봐주셔서 사랑하고 고맙다는 말을 전하고 싶고, 제게 길을 열어주시는 하나님께 무한한 감사를 드리며 이 감사의 글을 마칩니다.